面倒なので片電源での話にします(負電源を0Vとする)。 以下で電源と言った場合は、全部正電源のことです。

最近は電源電圧の低下に伴って入力も電源電圧いっぱいに振れるオペアンプが多くなってきています。 出力がレール to レールで、入力が0Vから、というオペアンプは結構昔からあった気がします。 出力をレール to レールにするのは簡単で、出力段をMOSFETのコンプリメンタリープッシュプルにすればOKです。 ただし、ソースフォロアではなく、ソース接地で。 要するにC-MOSロジックICの出力段と同じです。 実際、HレベルもLレベルも中途半端なTTLにくらべ、ロジックICのHCシリーズなんかはか なり昔から出力レール to レールと言っていい性能になっていました。

一方、入力の方ですが、0Vから可能にするには、N型のJFET・P型のMOSFETのいずれかにすればOKです。 N型JFETは、電圧の高いほうからドレイン・ソース・ゲートとして使う必要があり、ゲートが入力です。 MOSFETについてはゲートが絶縁されているのであまりそういう制限はありませんが、普通はP型ならばソースよりもゲートの電位を低くして使います。 どちらも、ゲート電位はゲートの耐圧を越えない限り、どこまでも下げられますから、入力0Vからが可能になります。

しかし、ゲート電圧を電源の方へ近づけていくと、JFETではやがてゲート電位がソース電位を超え、ゲートに電流が流れ始めてしまいます。 P型MOSFETの場合は、ソースが電源につながれているので、ゲート電圧を上げていくと、ゲート−ソース間電位差が小さくなっていき、Vthを割ると電流が流れなくなります。 入力の差動増幅器を構成するMOSFETのゲート−ソース間の電位差が両方ともVth以下になってしまえば、入力がどう動いても出力は出てきません。 したがって、このままでは入力レール to レールにはならないのです。

入力が差動でなくてよいのなら、一番簡単な入出力レール to レールアンプは74HCU04でしょう。 反転入力しかありませんが、+入力をスレッショルド電圧(ほぼVddの1/2)に固定してあると思えば、片電源のオペアンプのように使えます。 ただ、ひとつ欠点があって、アナログアンプとして使う場合は入力電圧はスレッショルド電圧付近をうろうろしますから、盛大な貫通電流が流れます。 でもちゃんと入出力レール to レールになっています。

入力を差動増幅器で構成したいのなら、何か対策を考えなければなりません。 簡単なのは入力0Vからは大丈夫なのだから、入力を0Vに対して抵抗か何かで分圧してゲートに入れる方法。 10MΩとかで分圧すればまあ一応は動きます。 オープンループゲインが半分になりますが、通常のNFBをかけた使用ではほとんど問題にならないはず。 ただ、やはり分圧抵抗の分だけ入力インピーダンスが下がっておもしろくありません。 実際、市販されているオペアンプの規格を見ると、入力リーク電流がpAの単位ですから、この方法ではありません。

となると、より高い電源を作るか、入力差動段を2個用意して合成するか・・・。 前者はインバーターかチャージポンプを使えば実現できます。 チャージポンプならインダクタがいらないので、チャージポンプの方が向いてるでしょう。 これはJFETでも使えます。 後者はMOSFET専用で、ある程度の電圧を超えると電流が流れてしまうJFETでは使えません。 N型MOSFETで差動増幅段を作ると、入力0V近辺に不感帯ができますが、P型とは逆に電源電圧いっぱいまで動作するようになるので、P型とN型の出力をうまく合成します。 この「うまく合成」が意外に難しいのですが。

どっちにしろ、こんな面倒なことはさすがにやってないよなぁ、もっと頭のいい人がすごい回路を考えているに違いない、と思って調べてみると・・・。

・・・マジデスカ。

ということで、実際にどうなってるかシミュレーションしてみよう、というのがこのページの趣旨です。 前者はまあチャージポンプさえ作れればどってことないので、後者の方で。

バイポーラトランジスタについては書きませんでしたが、バイポーラでも入力にエミッタフォロアを追加してレベルシフトしている例がロームの用語集に載っています(レール to レールではありませんが)。 また、リニアテクノロジーの入出力レール to レールオペアンプLT1801のデータシートにも簡略回路図が載っていて、こちらの入力は抵抗負荷の差動増幅器に直結されています。 トランジスタのVce(sat)が小さければ実現できそうですが、自信ないです。 出力段はエミッタフォロアではなく、エミッタ接地になってます。 こうしないと出力がレール to レールにならないからですね。

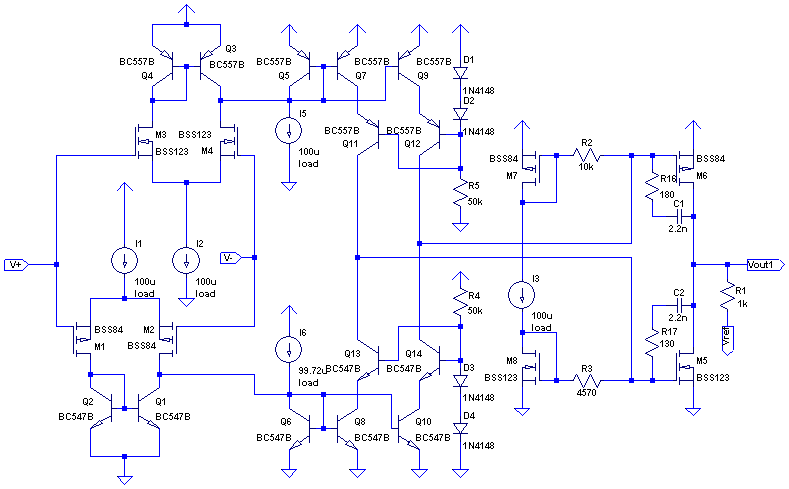

先に「簡単」と言い切ってしまった出力段から。

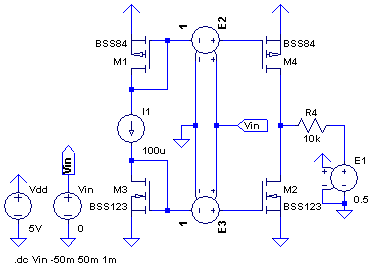

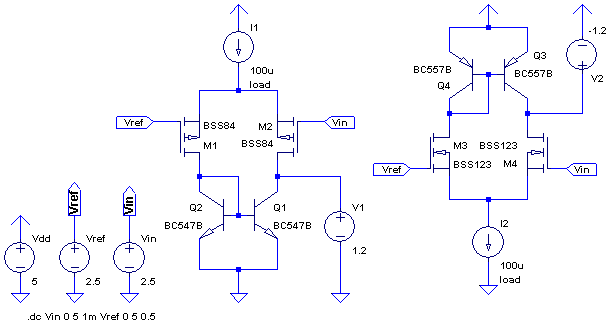

シミュレーションにはリニアテクノロジーが無料で配布しているLTspiceを使用します。 LTspiceについてはYahoo!さんなりGoogleさんなりに聞くといくらでも出てくると思うのでそちらを参照してください。 で、無料なのはすばらしいのですが、使えるデバイスモデルが少ないのですね。 日本のFETは全滅です。 また、ディスクリート部品のMOSFETはパワーMOSFETが多くて、こういう小信号増幅には使いにくいです。 ということで、なるべくゲート容量が軽いMOSFETを選んでみました。 P型がBSS84、N型がBSS123になりました。 電源はロジックICといっしょに使うことを前提として5Vで。

出力段はもうそのまんまです。MOSFETのソース接地コンプリメンタリーSEPPです。 ソースフォロアではレール to レールにはなりません。 ソースフォロアの場合はVdd側にN型MOSFETが来ますが、出力がVddのとき、言い換えるとソースがVddのとき、ゲートはそれよりVthだけ高い電位になっていないと電流が流れません。 しかし、VddよりVthだけ高い電位ということは電源電圧を超えてしまっています。 これはチャージポンプでももってこないとムリですね。

したがってソース接地で作ります。 基本はCMOSロジックICの出力段と同じで、Vdd側がP型、グランド側がN型です。 後ろにVddの0.5倍の電圧源がありますが、これは中点電位を作って負荷をつなぐためのもので、負荷が10kΩになっています。 したがって、実際の出力はMOSFETの端子そのもの(抵抗の左側)になります。

先ほど、74HCU04だと盛大な貫通電流が流れると書きましたが、それはバイアスを設定していないからです。 ソースフォロアやエミッタフォロアでは、上下の出力デバイスの入力端子の電位差が一定になるようにバイアスを作ります。 しかし、ソース接地のMOSFETプッシュプルでそのままこれを使うと、電源電圧が変わるったときにバイアス電流が大幅に変化してしまって具合が悪いです。 そこで、ソースがつながっている電源電圧側からの電位差が一定になるようにバイアス電圧を作ります。 早い話がゲート−ソース間電圧が一定になるようにバイアスを決めることにします。

バイアスを作っているのが左側の2個のFETです。 FETはゲートとドレインをつないで、ドレインに電流を流すと、ゲート−ソース間電位が勝手に「その電流になるはず」の電圧になります。 FETが飽和領域で動いていて、ソースを電源に直結してあれば、この電圧を他の「特性のそろった」FETのゲートにかければ、そのドレインにはだいたい同じ電流が流れます(実際にはドレインの電位によって若干変動する)。 要するにカレントミラーの動作なのですが、これをバイアスに利用しています。 今回は低消費電力オペアンプを想定して、100uA流しています。

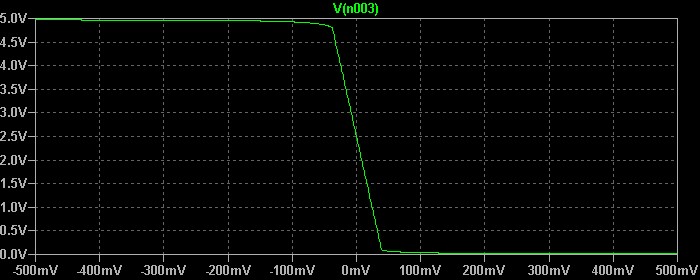

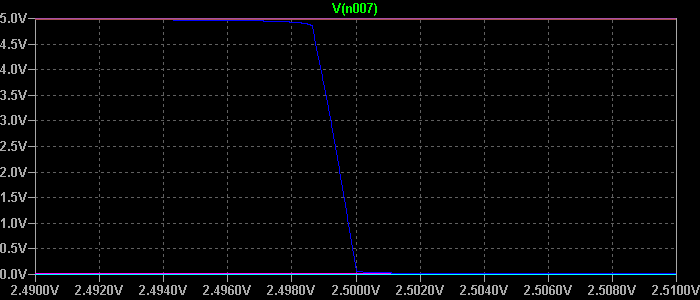

あとは入力信号に応じてこの電圧を上下させればよいので、電圧制御電圧源を直列に放り込んであります。 入力電圧を-50mVから50mVまで振れば、ゲート電圧も50mV上下します。 ゲート電圧が上がると、P型の電流は減少し、N型は増加するので、出力電圧は下がります。 つまり、反転増幅器になります。 ソースフォロアとは逆ですね。 実際に電圧を振ってみたのがこれ。

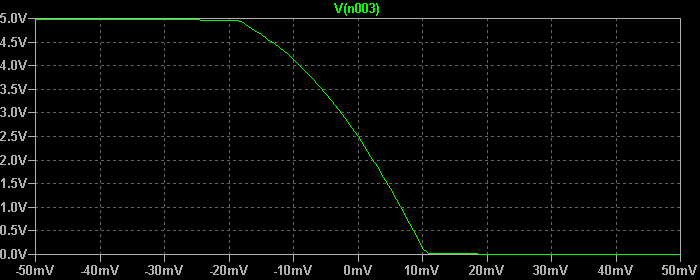

出力はほぼ電源電圧まで振れています。 出力レール to レールあっさり達成。 なんか入力0mVから左と右でカーブが違いますが、これはN型のほうが相互コンダクタンスが高いからですね。 このままでいくと偶数次のひずみが大量に出そうなので、電圧源の倍率をN型は0.5倍にしてみます。

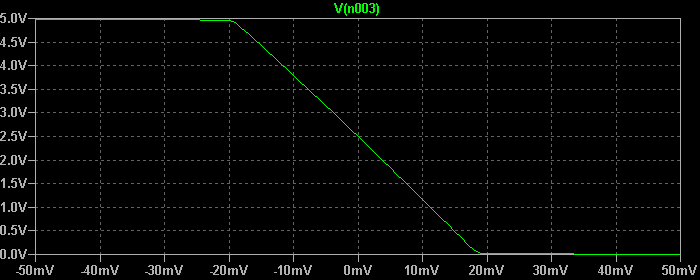

ほぼ真っすぐになりました。 すばらしい。 交流信号を入力するともっと正確に調整できますが、あとでやることにします。 ここで負荷を重くしてみます。 負荷を1kΩにするとこんなんなります。

横軸が変わっているので注意してください。 -0.5Vから0.5Vまで振っています。 微妙に電源電圧まで振れていませんが、これはMOSFETの内部抵抗に限界があるからです。 見かけの出力インピーダンスはNFBをかけると下がりますが、電源電圧近くではFETの内部抵抗が限界になります。 したがって、電流を取れば取るほど、出力電圧は電源電圧から離れ、レール to レールとは言えなくなってきます。 これはまあ、こんなもんというか、仕方ないというか。 実際のオペアンプの規格表にも、何mAまでとったときは何mVまで、という規定がされているはずです。

それと、グラフ中央でぐにょんと線が曲がっていますが、これは出力段がB級動作しているからです。 この曲線は3次曲線に似ていて奇対称なので、ひずみは奇数次になるはずです。 今回は低消費電力オペアンプを想定しているのでこうなるのですが、ひずみを減らしたいのならバイアス電流を増やして、AB級、さらにはA級で動作させればOKです。 負荷が1kΩで両端の電圧が±2.5Vなので、電流は最大2.5mA流れます。 そこで、バイアスを2.5mAにしてみると、

ほぼA級動作になるので、このとおり真っすぐになります。 出力段だけでも結構いじりがいがありますね。

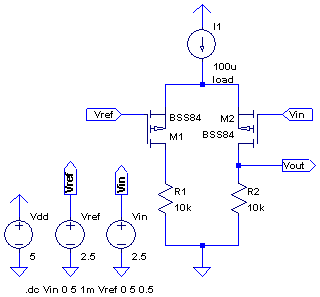

まず教科書どおりの回路から。 0Vからの入力に対応するため、P型MOSFETで作ってみます。

出力インピーダンスが高いので、今回は負荷はつなぎません。 また、電流源は常に指定された電流を流すのではなく、指定された電流になるように抵抗値を制御するような感じになっています(能動負荷)。 したがって、指定された電流に達しなくても、両端の電位差が0になれば、それ以上無理に電流を流すようなことはしません。 Vrefを0Vから5Vまで0.5Vずつ振り、それぞれVinを0〜5Vまで動かしたグラフがこれ。

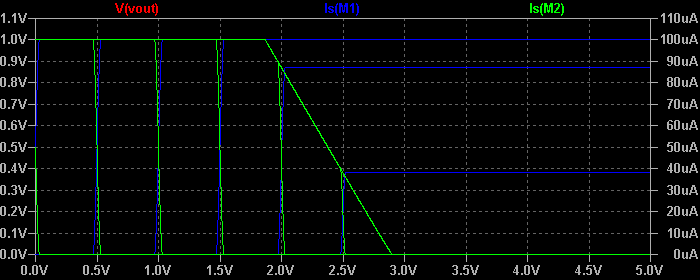

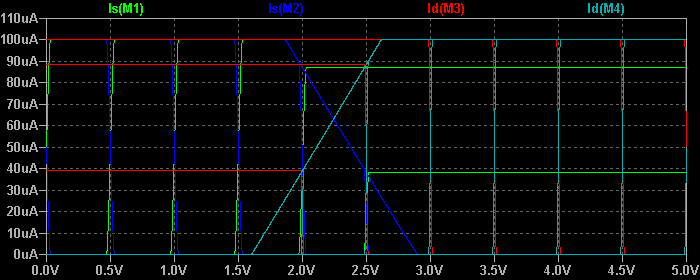

ふたつのFETのソース電流(=ほぼドレイン電流)を見ています。 グラフにはVoutも表示しているのですが、M2を流れる電流×10kΩが出力電圧になり、100uAで1Vになりますが、縦軸の100uAと1Vがちょうど同じ位置になっているせいで、ソース電流とぴったり重なって見えません。

一番左側で交差している線がVrefが0Vのときです。 この通り、入力0Vからしっかり動いています。 右にいくにしたがい、Vrefが0.5V・1.0Vですが、2.0Vあたりで途中でM2に電流が流れなくなって、合計した電流が90uA弱しか流れなくなります。 さらにVrefをあげていくと、合計電流はどんどん小さくなり、2.8Vを過ぎたあたりでまったく電流が流れなくなります。 したがって、プラス側は電源いっぱいまでの動作はしません。

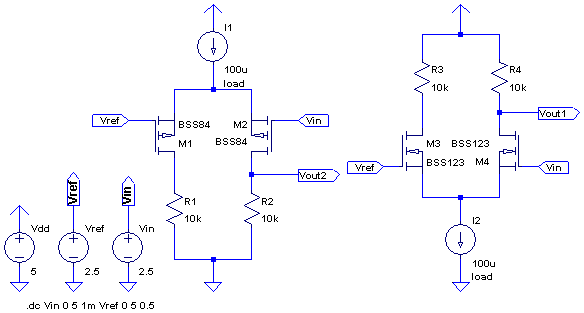

同じ回路をN型MOSFETでも組んでみます。 上下ひっくり返して、FETを入れ替えるだけ。

同様に電圧を振るとこうなります。 P型といっしょにプロット。

ちょっと見にくいですが、緑と青がP型、赤と水色がN型ですね。 N型は逆に電源電圧に近いところで正常に動作し、0V付近では動きません。 2.25V近辺でP型とN型が主役交代しています。60uAちょっと流れていますから、両方足して125uAくらい。 なんとか動くかなー、っていう感じですか。

この2つを足せばいい具合になりますが、足し算にオペアンプを使うわけにはいかない(笑)ので、別の方法を考えなければなりません。 まず、電圧で足すか、電流で足すか、ですが、電圧は直列にしないといけないのに対し、電流はあるノードに電流を押し込んでやれば足し算できますから、電流で足した方が楽です。

このときひとつ問題があって、動いてない側の出力電流が0だ、ということです。 動いている場合の0は負側に振り切った場合ですから、「動いてない」=「負側に振り切り」になってしまいます。 動いていないときは「出力ニュートラル」、つまり、Vin=Vrefのときと同じになっていないとうまく足せません。 もし、Vin=Vrefのときに電流が0になってくれれば、「動いていない」=「Vin=Vref」なので、うまく足すことができます。 そんな回路が実はあります。 なんでこんな回路があるんだろうとずっと思っていたんですが。

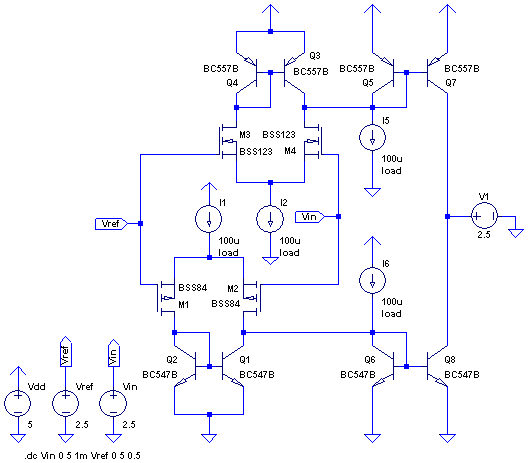

いわゆるカレントミラー負荷っていうやつです。 カレントミラーはFETで作ってもいいんですが、Vthが高めで電圧の設定に苦労しそうなので、カレントミラーを作ったときに基準側の電位がVBE=約0.6Vになる、バイポーラトランジスタを使いました。 トランジスタの選択は例によってIcでソートして上のほうに出てきたやつを適当に。 出力には電圧源が直結してありますが、電流出力なのでこれでいいのです。 壊れたりしません。 電流源というのはそういうものです。 N型の方は負の電圧設定で、±がわざわざ逆さにしてありますが、これは差動増幅器から電流が出る方向を+にしたかったからです。 まあ、グラフ側でマイナスを付けてもよかったんですけどね。 電源側につないでるのは、電源電圧が変わっても動くようにです。

カレントミラーの説明は他を見てもらうことにして、差動増幅器に突っ込んだ場合にどう動くかを考えてみます。 ベースとコレクタがつながっている方が基準側で、基準側のFETは自由に電流の大きさを決めることができます。 反対側は従属側で、基準側に流れた電流と同じ大きさに強制的に「制限」されます。 今は電圧源がつながっていて電流値に制限はありませんから、結局、基準側と同じ大きさの電流が強制的に流れます。 一蓮托生。

とりあえず右側(N型)の差動増幅器を考えると、左右のFETがバランスしているときは、元々流れている電流が同じですから、両方に50uA流れてめでたしめでたしです。 出力の電圧源との間で電流の出入りはありません。 もし、基準側のFETの電流が増えると、それにつれて従属側のトランジスタに流れる電流も増えますが、従属側FETの方はむしろ電流が減っているはずなので、余った分がおえっっっと出力に吐き出されます。 逆に、基準側FETの電流が減ると、従属側のトランジスタに流れる電流が減ってしまいますが、従属側FETはもっと電流を欲しがりますから、出力につながれた電圧源からずずず〜っっと電流が吸い込まれます。

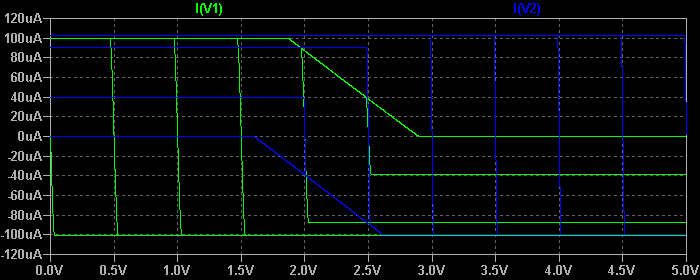

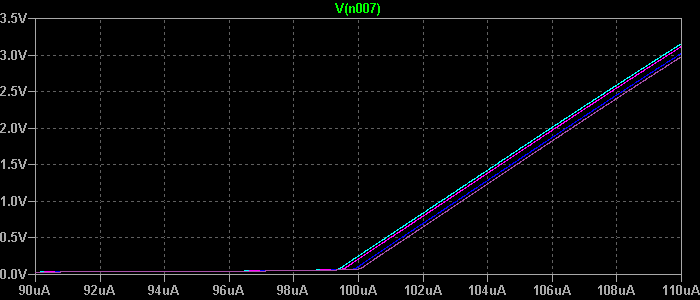

結果はこんな感じ。

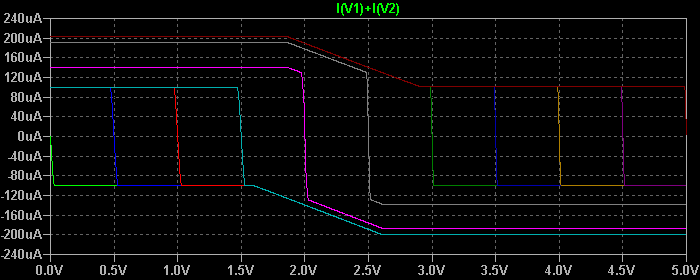

緑のほうがP側の差動増幅器、青のほうがN側の差動増幅器の電流出力です。 縦軸の中央が0であることに注意してください。 吐き出される方(+)は分かりやすいのですが、吸い込む方はイメージしにくいですね。 でも実際に吸い込んでます。 電流マイナスになってます。 動いているときは±100uAで動き、動いていないときは見事に0です。 これならそのまま足せます。 実際にグラフ上で足してみるとこうなります。

見事です。ちゃんと0uAをセンターにして上下に振ってます。 入力レール to レールが見えてきました。 P型もN型も動いている部分と、どちらか片方しか動いていない部分で傾きが違っています。 これは、動作している領域によってゲインが違うということを意味しています。 したがって、この領域をまたいで電圧が動くとひずみが増加します。 先のEDNの記事にも書いてありましたが、非反転である程度の振幅の信号を扱うとこの領域をまたいでしまい、ひずみが増えます。 反転構成にすれば、+入力を0.5Vddに固定して、イマジナリアースで−入力もほぼその付近で動きますから、ひずみ率に関しては圧倒的に有利です。

さて、次の問題はどうやって足すか、です。 電流出力なのでぽちっとつなげばいいのですが、電圧が異なっているのでそのままではつなげません。 ここでまたカレントミラーを利用します。 出力電流をカレントミラーの基準側に流し、従属側のコレクタから取り出します。 入れたものが出てくるだけですが、従属側のコレクタは飽和電圧を上回っていれば好きにできます。 これでぽちっとつなぐことができます。

でもちょっと待って。 さっき、電流が出たり入ったりするようにしませんでしたか? ということは、このままカレントミラーに入れると、正負どちらかはトランジスタのエミッタを逆流することになります。 もちろんそんなことできませんから、もう一回オフセット電流を流しなおします。

PNP側のカレントミラーは電源から電流を取ることしかできませんから、差動増幅器から電流が出てきたら、それを電位が低い側にバイパスしてやります。 逆に、NPN側のカレントミラーは電流を0V側に流すことしかできませんから、差動増幅器が電流を欲しがったら、電位が高い側から電流を流し込んでやります。 電流源の値は流れる電流の最大値にしなければなりませんから、この場合は差動増幅器の基準電流100uAと同じになります。 今はさらっと電流源で書いてしまいますが、ICの中ではこの電流も基準電流を作っているカレントミラーで作れます。

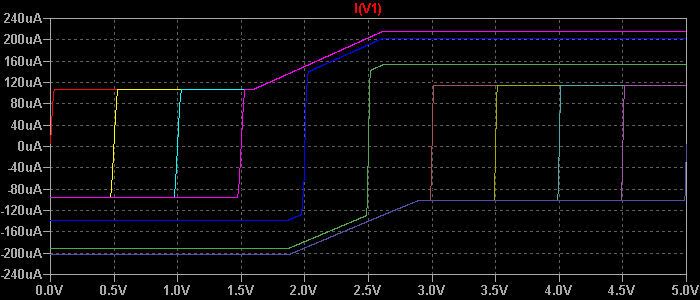

差動増幅器のカレントミラー負荷の出力を、次のカレントミラーの基準側に突っ込みますが、そのときに基準電流に相当する分を足し引きします。 電圧源V1は電流測定のために置いてます。 実際に動かしてみるとこんな感じ。

グラフ上で足した図と比べると上下(つまり符号)が逆になっていますが、それ以外はほぼ同じになりました。 これで入力レール to レール達成、と思っていいでしょう。

カレントミラー負荷で差をとって、オフセット電流をもう一度足して、さらにカレントミラーに流して、と面倒に見えます。 しかし、カレントミラー負荷は出力0と動作していないときを同じ状態にするため、後段のカレントミラーは電圧を合わせるため、そしてオフセット電流は後段のカレントミラーを動かすためにあります。 それぞれ役目があります。 頭のいい人が考えれば、もっとスマートな回路ができる気がしますが。

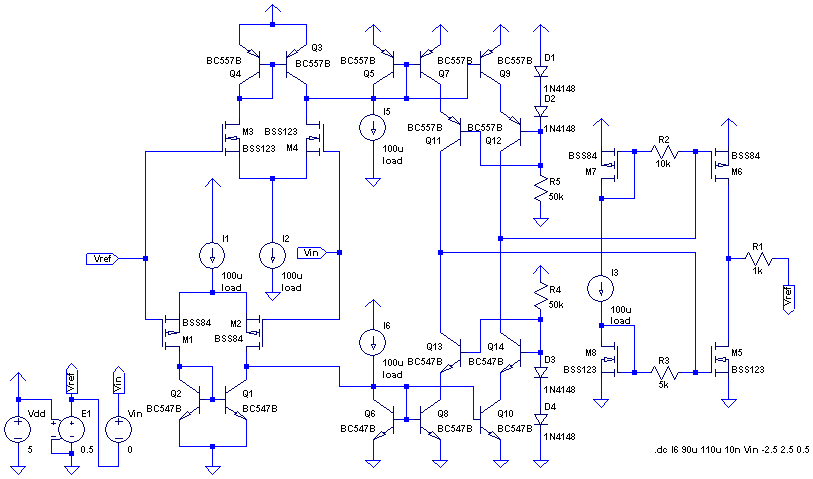

この後ろに先ほどの出力段をつなぎます。 P型とN型で電圧が違うので、カレントミラーの従属側をもう一組作って、それぞれを出力段のP型とN型のゲートにつなぎます。 出力段の入力に使っていた電圧源のところを置き換えるわけですが、差動段が電流出力なので、電圧源が入っていたところに抵抗を置き、電流を押し引きして電圧に変換します。 100uAの変化を1V程度に変換したいので、10kΩを入れることにします。 また、N型の電圧源の係数をP型の半分にしていたので、N型は抵抗値を半分にして5kΩを入れてみます。

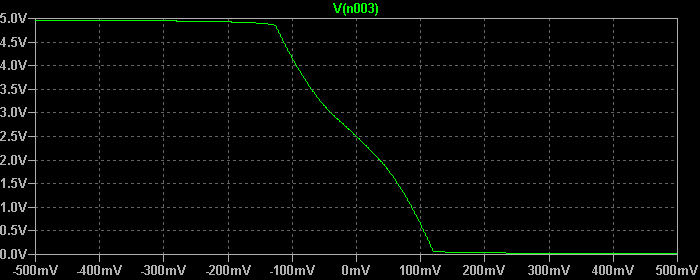

VrefはVdd/2になるようにしてあります。 +入力には別に電圧源をつなぎました。 負荷は1kΩ。 実際に動かすとこんな感じ。

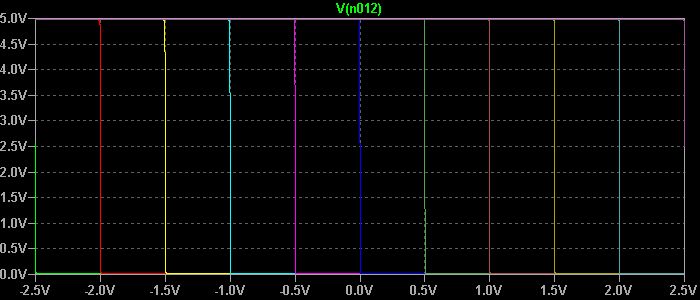

入出力レール to レール、達成です。 でもよく見ると、一番左にあるはずの緑の縦線がありませんね。 入力2.5V付近を拡大してみます。

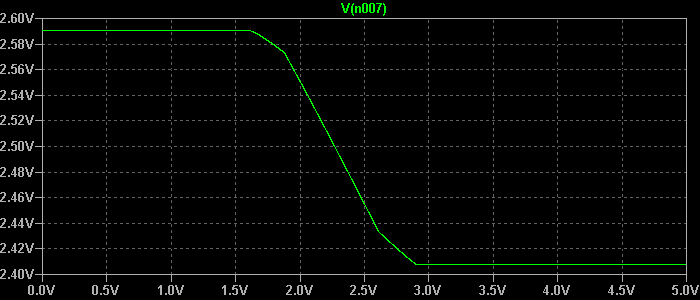

この線は正相入力電圧が2.5Vのときのものです。 なので、Vin、つまり逆相入力電圧が2.5Vのときに出力が中点、今はVddが5Vなので2.5Vになってほしいのですが、左側にずれています。 つまり、マイナス方向に盛大にオフセットが発生している、ということです。 オフセットがあるなら調整してしまいましょう。 そのためには、N・Pどちらかの基準電流をどこかで調整すればOKです。 ここではI6を調整してみます。 差動増幅器の両方の入力を束ねて、I6を90uAから110uAまで動かしてみます。

横軸はI6の電流、縦軸は出力電圧で、パラメータは束ねた入力の電圧、つまり同相電圧です。 これを見ると108uAくらいでオフセットが0になりそうです。 I6を108uAに調整し、同相電圧対出力電圧を見ると、

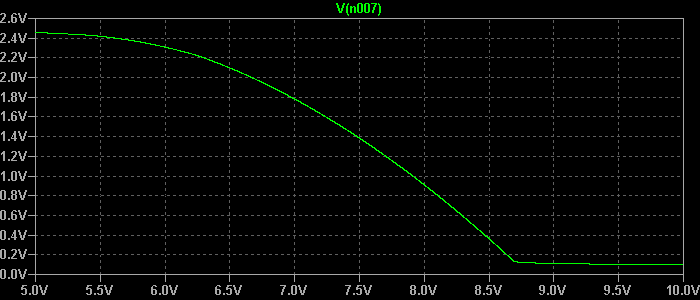

全同相電圧範囲で出力電圧2.5±1Vに入りました。 電源電圧を振らないならこれでも実用になると思いますが、電源電圧を振ってみるとこうなります。

両方の入力は束ねてVdd/2を加えています。 出力の負荷抵抗もVdd/2に接続しています。 横軸が電源電圧で縦軸が出力電圧です。 電源電圧を上げれば中点電位も上がるので、出力電圧も上がっていってほしいのですが、逆に下がっています。 どうしてでしょう?

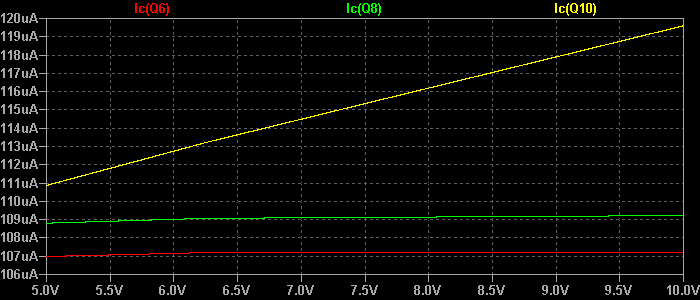

下側カレントミラーの各コレクタ電流を見てみると、

入力はVdd/2に接続してあります。 横軸は電源電圧です。 基準トランジスタQ6の電流はほぼ一定、N型をドライブしているQ8のコレクタ電流もほぼ一定ですが、P型をドライブしているQ10の電流は電源電圧とともに増えてしまい、理想的なカレントミラーから動きがずれています。

出力段のN型のバイアス電圧はグランドから決まり、P型のバイアス電圧は電源電圧からの電位差で決まるので、Q8のコレクタ電圧はほとんど変わらないのに、Q10のコレクタ電圧は電源電圧が上がった分だけ上がってしまいます。 活性領域ではコレクタ電位が多少変動してもコレクタ電流は一定で、これをカレントミラーに利用しているわけですが、実際にはコレクタ電圧が上がると若干ですがコレクタ電流が増えていきます。 いわゆるアーリー効果。 これがQ10のコレクタ電流が増えていく原因です。

上側のカレントミラーでも同じことが起きます。 今度はN型のバイアス電圧が電源から見て下がっていくように見えるので、N型をドライブしているQ7の電流が増えていきます。 PNPとNPNのペアはQ7とQ8、Q9とQ10なので、電源電圧が上がるとQ7のコレクタ電流が増えてN型のゲート電圧が上がり、Q10のコレクタ電流が増えてP型のゲート電圧は下がります。 これはどちらもドレイン電流を増やす方向なのである程度は打ち消しあいますが、実際にはPNP型とNPN型の特性・・・活性領域のVce-Ic特性・・・が揃っていない分が誤差になって出力に現れます。

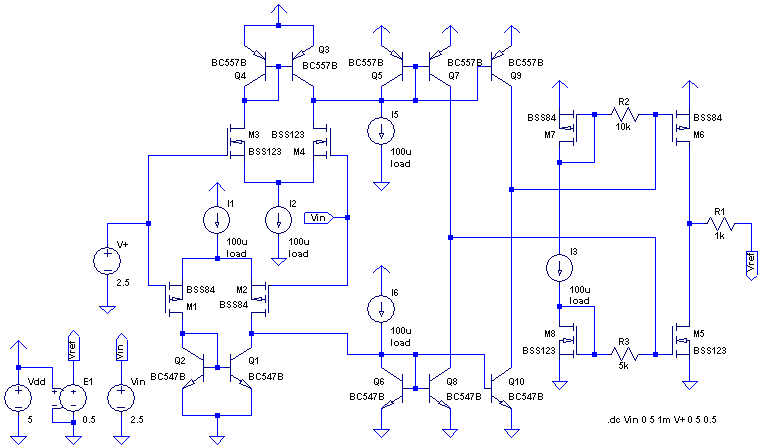

ではどうしましょう。 コレクタ電圧が動いてしまうのがいけないので、コレクタ電圧を固定してしまえばいいのです。 どうやって? 「トランジスタのVbeがほぼ一定」「エミッタ電流はほとんどそのままコレクタ電流になる」「コレクタ電圧は自由」という性質を使えばできそうな気がします。 つまり、トランジスタを追加し、そのベース電位を固定して、エミッタをカレントミラーにつなげば、カレントミラーのコレクタ電圧はほぼ一定にできます。 しかも、カレントミラーの電流はすべて追加したトランジスタのエミッタへ流れますから、ほとんどそのままコレクタから出てきます。 これなら、新しく追加したトランジスタのコレクタ電圧が多少動いても、カレントミラーの電流は影響を受けなさそうです。

Q11・Q12・Q13・Q14が新しく追加したトランジスタです。 ベース電位はグランドあるいは電源から、PN接合の電圧降下2個分、約1.2Vに固定されています。 したがって、エミッタ電位は約0.6Vに固定され、ここがカレントミラーの出力となるコレクタにつながっています。 カレントミラーのコレクタに流れた電流は、他に行き場がないので間違いなく新しく追加したトランジスタのエミッタに流れます。 ここからベース電流を引いたのがコレクタ電流ですが、トランジスタがきちんと動いていれば、ベース電流はコレクタ電流の1/hFE倍ですので、エミッタ電流はほとんどそのままコレクタに出てきます。 レベルシフタとか、レベルアジャスタとか呼べそうな動作になります。 世の中ではカスコード回路と呼んでる気がしないでもないです。

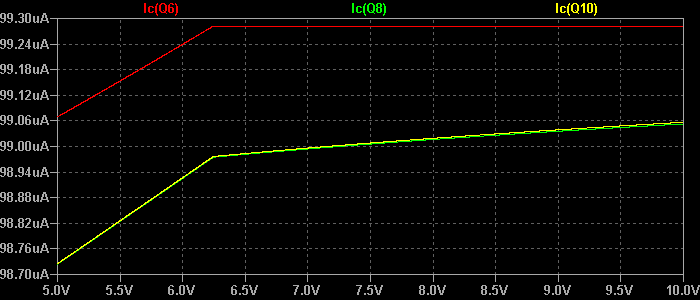

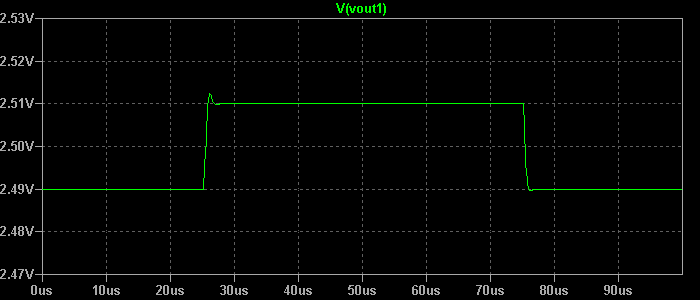

早速先ほどと同じ条件、つまり、入力を束ねてVdd/2につなぎ、電源電圧を振ってカレントミラーのコレクタ電流を見てみると、

先ほどとは縦軸のスケールが全然違うことに注意してください。 さっきは1uA/div、このグラフは0.06uA/divです。 Q8とQ10のコレクタ電流はほとんど一致し、電源電圧の影響も最小限に抑えられている様子が分かります。 オフセット電圧を調整するために、Vdd=5V、同相電圧をパラメータとしてI6を振ってみます。

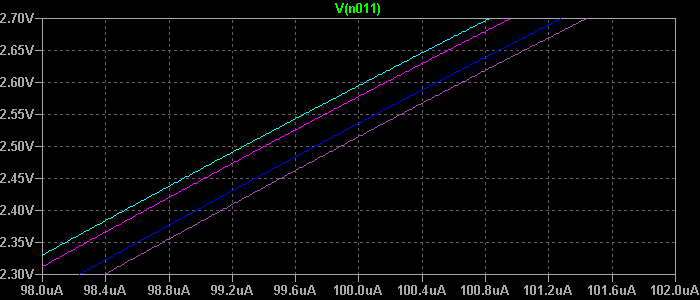

青線がVin=2.5Vなので、I6を99.7uAに設定することにします。 この状態でVddを振ってみると、

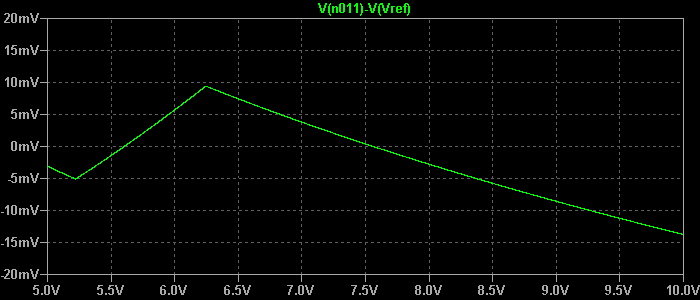

入力は束ねてVdd/2に、縦軸は出力電圧からVrefを引いたもの、つまり中点電位からのずれです。電源電圧を振っても±15mVに収まっています。

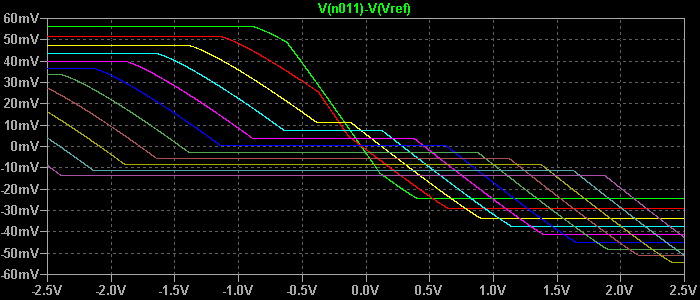

上の回路のように、VinがVrefに対して相対的に動くようにし、入力は束ねてVinにつなぎ、VinをVref±2.5Vの範囲で振ってみました(つまり、同相電圧をVdd/2±2.5Vで振ってみた)。 パラメータはVddで、左上の緑線が5V、0.5Vずつのステップで、一番左下が10Vです。 この範囲で±60mVに収まっています。 ただし、この特性は負荷1kΩをつないだ状態の特性です。 負荷抵抗を大きくするとオフセットは大きくなる傾向があるので注意してください。

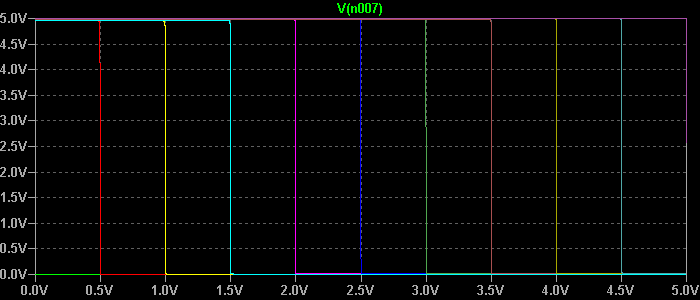

電源電圧が5Vのときの入出力特性を見ると、

こんな感じ。 横軸は逆相入力電圧ですが、Vdd/2からの電位差になっています。 左端・右端にきちんと半分だけの縦線が出ている点に注目してください。 正真正銘、入出力レール to レール達成です。 こうして実際に動かしてみると、カレントミラーがいかに重要かがよく分かります。 アナログICの中身って基本的に電流をうまくやりくりして作られているんですね。

このアンプは差動対が2組あるので、両方の差動対が動いているとき、N型だけ動いているとき、P型だけ動いているときでゲインが違います。 また、出力段もAB級のSEPPなので、上下両方のMOSFETが動いている部分、P型のみ、N型のみで動いている部分でゲインが違います。 また、出力電圧や負荷によってもA級→AB級→B級と動作が変わります。 めんどk・・・んがんぐ。

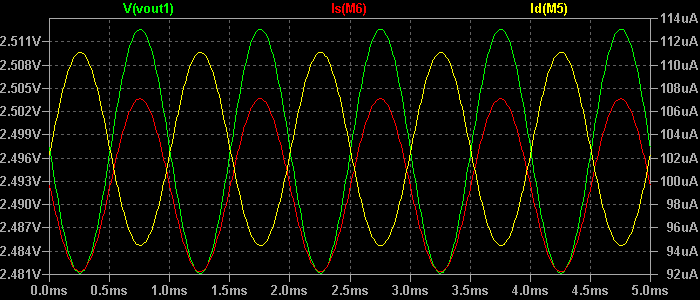

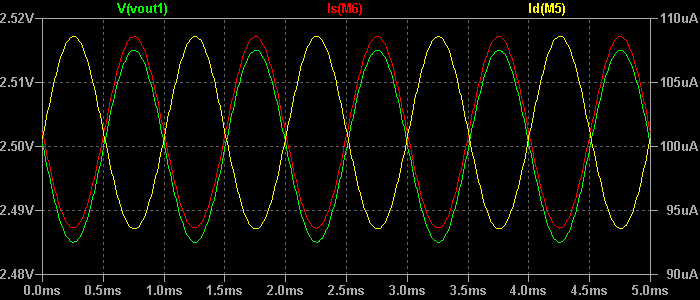

まず出力をA級動作させます。 バイアスが100uAで、負荷が1KΩなので、中点電位から±100mVまでの範囲でA級動作します。 2.5Vを中心に振幅10uV(20uV p-p)の1kHz正弦波を入力してみました。

緑の線が出力電圧で、約30mV p-p なので1500倍です。 赤の線がP型、黄色の線がN型MOSFETの電流を示していて、A級動作しているのが分かります。 本当は100uAを中心にクロスするはずですが、きちんと調整していないのでずれています。 全高調波ひずみ率(THD)は0.09%。

温度が変われば動作点なんてすぐ動く(温度が動いても動作点があまり動かないように作るのがいい設計なわけですが)ので、精密にあわせてもあまり意味がないのですが、せっかくなのでもう少し細かく調整してみます。 I6をスイープして、99.723uAのときに上下のFETの電流が等しくなりました。 出力は当然ちょうど2.5Vになります。 抵抗の方は .step ディレクティブと .four を使って追い込みましたが、ノイズの影響が出るのか、計測期間が短いと1Ω単位での設定は意味がないようでした。 ということで、R3を4560Ωにしました。 結果はこうなりました。

きれいにA級動作しています。 2つのFETの電流は中央で交わり、同じ振幅で動いています。 ひずみ率は0.018%まで減少しました。

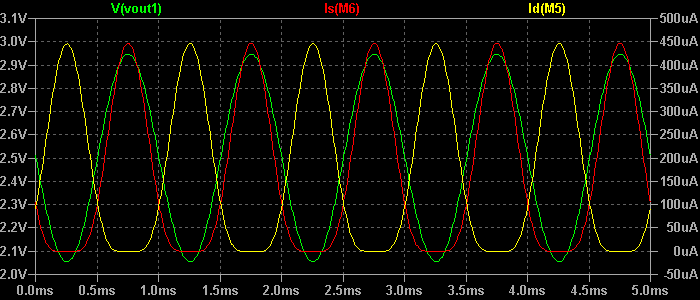

次。出力が±100mVを超えるとAB級になります。 1500倍なので入力は±66uVになります。 試しに±300uVほど入れてみました。

典型的なAB級動作。 出力電圧は893mV p-p なのでやはり約1500倍。 THDは0.61%。 さらに電圧を上げていくとB級動作になります。 ±1mVを入れてみました。

4.22V p-p出ているので約2100倍です。 A級に比べかなりゲインが大きいです。 A級動作している部分はせっかくP型が吐いた電流をN型が吸ってしまいますが、B級動作している部分ではすべて出力に出てくるので、それがゲインの差になって現れています。 ただし、波形を見れば分かるようにひずみも相当多いです。 LTspiceに計算させてみると8.66%と、10%に迫るひずみ率です。 スルーレートが追いついていないようにも見えますが、100Hzにしても同じような波形だったので、出力段のひずみが原因です。

出力段の設計中に直流特性をさらっと調べましたが、負荷を重くしたときに直線から外れいてる部分がそのままひずみになっている様子が分かります。 傾きが急になる方向なので、ゲインが増え、波形の上下が引き伸ばされるようなひずみ方になります。 これはソース接地の弊害とも言えるかもしれません。 その代わり、ソースフォロアと違って電圧ゲインがあるので、NFBをかけて改善することになります。 嫌がる人がいそうですが、そういう人は出力レール to レールは使わない方がいい(ソースフォロアあるいはエミッタフォロアSEPPを使う)ということになるのでしょうか。

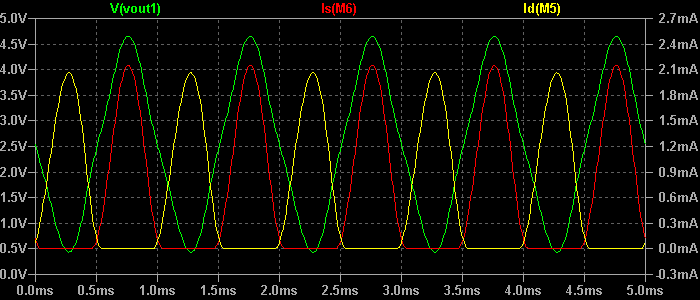

次。A級動作の状態で、入力にオフセットを入れると、出力電圧が上下します。 出力電圧が上がるとP型だけで動くようになり、下がるとN型だけで動くようになります。 ゲインが約1500倍なので、出力を2V上げ下げするのに必要な電圧は1.3mVです。 ここでは±1mVだけオフセットを加えてみました。 Vrefは2.5V、入力は1kHz・2.5V±10uVの正弦波、負荷は1kΩです。

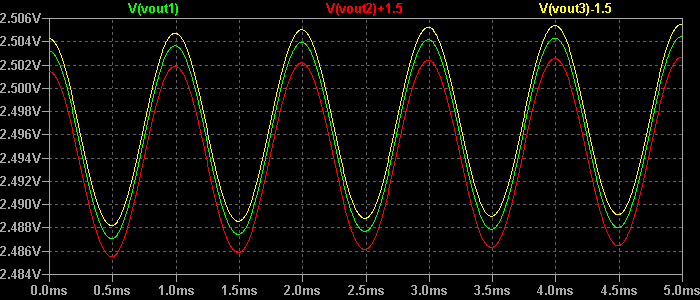

分かりやすいように同じ回路を3枚貼り付けて、オフセットを加えた入力を入れて、1枚のグラフにしてみました。 そのままだと振幅に比べて線が離れすぎて見にくいので、グラフ上でスケールを変えずに緑線へ寄せてみました。 緑線がオフセットなし、赤線は+1mVのオフセットで、出力は下側に動きます。 実際には0.4V程度を中心に動いています。 黄色線は-1mVのオフセットで、出力は上側に動きます。 実際には4.66V程度を中心に動いています。 こんな端でもちゃんと動くんだ・・・まあ、動くように作ったはずなので、動いてくれないと困るのですが。

緑が30mV p-pなので1500倍、赤が62mV p-pなので3100倍、黄色が66mV p-pなので3300倍です。 やはりA級動作している部分より、N型・P型シングルで動いている部分の方がゲインが大きくなります。

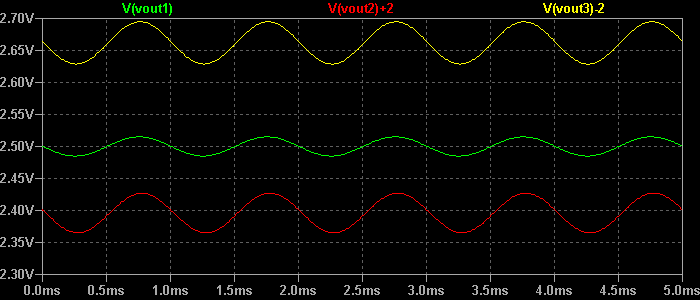

次。 入力段。正相・逆相とも同方向にオフセットを加えてやる、つまり同相電圧をそっくり動かすと、N型差動対のみ・P型差動対のみで動作させることができます。

緑が同相電圧2.5Vで、N型・P型の差動対が両方動いています。 実際には電源電圧5Vだと、N型もP型も完全には動ききっていません。 これは差動増幅器設計中のグラフを見れば分かります。 完全に動かすには6V程度必要のようです。 ゲインは1500倍、ひずみ率0.018%。

赤は同相電圧1Vなので、P型しか動いていません。 P型の方が相互コンダクタンスが低いようで、11mV p-p、550倍しかゲインが出ていません。 ただ、振幅が小さい分、ひずみ率は0.0055%まで減っています。 (オープンループ)ゲインが低いということは、NFBが減るということなので、NFBをかけてゲインを調整するとほぼ同じくらいの数字になりそうです。

黄色は同相電圧4VなのでN型しか動いていません。 245mV p-p、1250倍。両方動いているときより若干ゲインが減ります。 P型に比べてあまり減ってませんが、これは2.5Vのときに既にP型があまり働いてないということです。 これは直流解析時のグラフでだいたい想像がつきます。 ひずみ率0.015%。

なんとなく気になって、Q11あるいはQ13のうち、電流が流れている方のひずみ率を見ると0.001%前後でした。差動対ってこんなにひずみが少ないんですね。 ひずみ率の大小は、出力振幅の増加による出力段のひずみの増加の影響の方が、差動増幅段そのものより大きそうです。

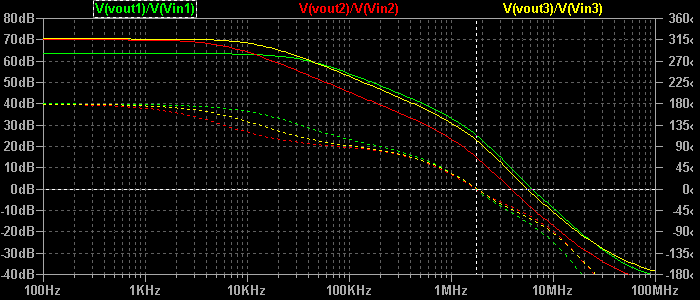

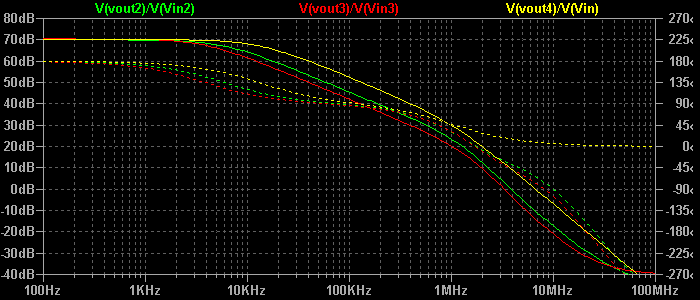

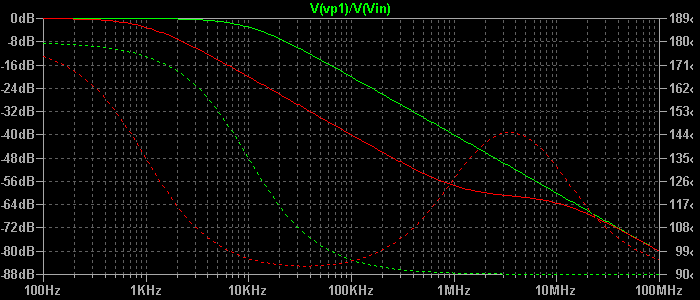

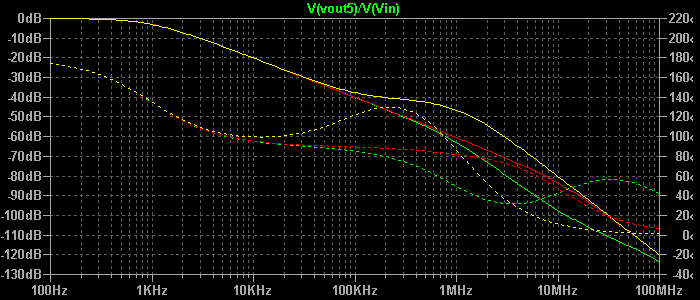

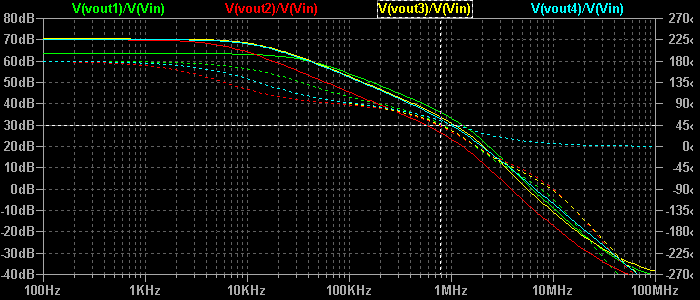

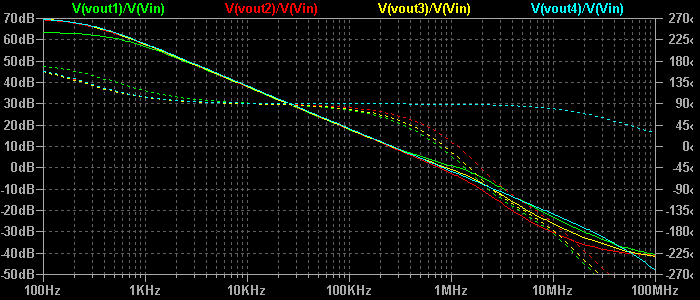

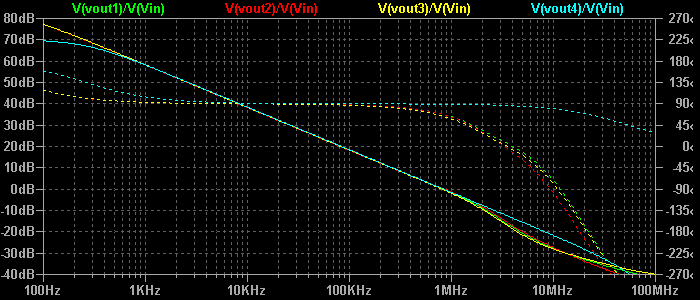

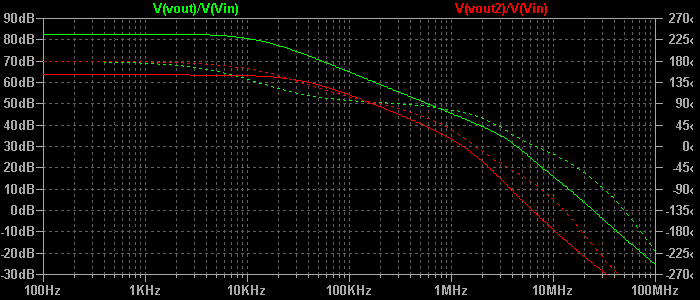

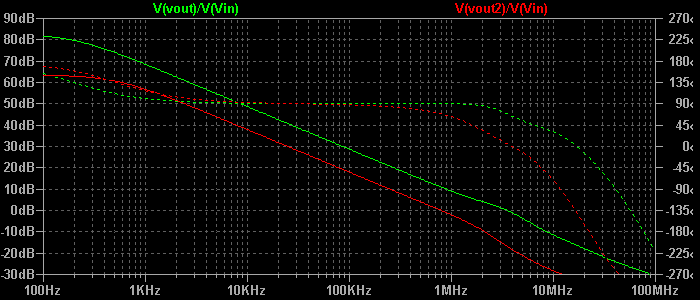

最後にNFBをかける上で避けて通れない位相補償です。 とりあえず周波数特性を見てみます。 入力段はN型・P型とも動いているときが一番ゲインが大きいので、同相電圧は2.5Vにして、オフセットを±1mV加えて、出力段はA級動作時、N型シングル、P型シングルの3通りを見てみます。 入力は10uV、負荷は1kΩ。

緑がA級、赤はN型シングル、黄色はP型シングルです。 オープンループゲインはシングル動作のときに約70dB、A級動作のときでも63dBくらい。 さっきP型とN型のバランスを調整したので、シングル動作のゲインはほぼ揃っています。 ただ、高域では意外にもA級動作時の方がゲインが高くて、位相が180度回るときのゲインは約25dB。 ftは4〜7MHz。 あまりよくないですね。 ソース接地の弊害なのか、電流をケチったせいなのか。

負荷を10kΩに変えるとこうなります。

負荷を10kΩに変えるとゲインが上がったように見えます。 しかし、第一ポールがしっかり低域に動くので、位相が180度回るときのゲインはほとんど変わりません。 とりあえず負荷1kΩで調整して、あとで10kΩでどうなっているか見ればいいでしょう。 シングル動作のゲインがやたら低くなっていますが、これは飽和してるからです。

位相補償の手順ですが、

という手順にします。 ポールの周波数はグラフの傾きが変わるところですが、正確に何Hzと言える人は少ないのではないかと思います。 というか、正確に言える人はこのページは多分見てません(笑)。 基本的に位相が45度回ったところなのですが、第2ポール以降は次々とポールが出てきてどこが第2ポールだかよく分かりません。 重要なのは第2ポールまでなので、簡単な回路を組んで近似曲線を一緒に表示すると楽です。 この回路の定数を行き当たりばったりで調整します。

近似曲線ができたら、これまた行き当たりばったりでポールになりそうなところに適当なコンデンサを入れて、曲線の変化を見ます。 全体が下に下がったらそこが第1ポールです。 高域だけ下に下がるようならそこは第2ポール以降です。

ポールの原因になっている場所がわかったら、位相補償コンデンサを入れやすそうな場所を決めます。 そこが第1ポールならラグリード補償、第2ポールならステップ補償をすることになるんでしょう、きっと。 この辺の用語はサーチエンジンに聞くととてもよいページを紹介してくれます。 詳しい数式も載っていますが、面倒なのでやはり行き当たりばったりで調整します。

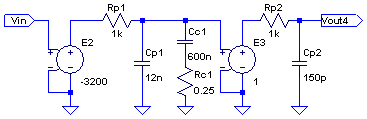

まずポールの位置を調べましょう。 そのためにはこんな回路を作ります。

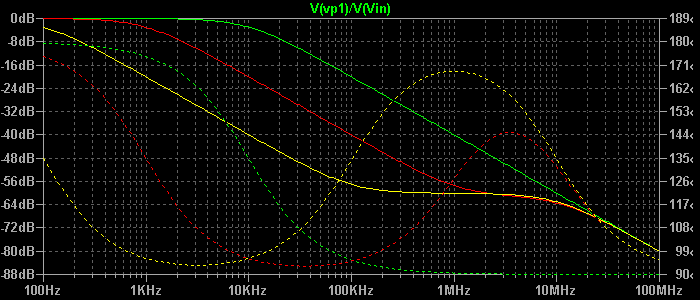

この周波数特性をいっしょにプロットして、定数を調整します。 倍率は周波数特性の縦軸をdBからLinearにすればすぐ分かります。 あとは行き当たりばったりで。 実際のプロットはこんな感じ。

Vout1を削ってしまったので、緑がN型シングル、赤がP型シングル。 周波数特性が伸びてるP型シングルに合わせてみました。 左側が第1ポールで、周波数は1/2πCRなので約13kHzです。 右側は第2ポールで、約1MHzです。

次にポールを探します。 ポールになりそうなところは、MOSFETのゲートか、トランジスタのベース−コレクタ間容量です。 まず入力のFETがポールの候補になります。 カレントミラー負荷の基準側はほぼ0.6V固定なので、基準側のFETはそんなに大きなポールにはなりません。 従属側は次段のカレントミラーの基準側につながっているので、やはりほぼ0.6V。 その従属側はカスコード回路で固定していて、カスコード回路はベース接地なのでやはり大きなポールにはならないでしょう。 その先のソース接地SEPP回路は反転増幅器なのでミラー効果があり、大きな容量に見えそうです。

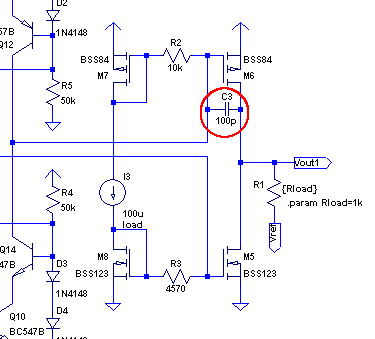

とりあえずここにコンデンサを入れてみます。 今はP型シングルを見ているので、M6のゲート−ドレイン間に100pFを入れてみます。

これで全体が下がればここが第1ポール、第2ポール以降が下がれば第2ポールです。

正解(笑)。全体が下がったのでここが第1ポールを作っています。 ちなみに、差動段のM4のゲート・ドレイン間に1nFを入れてみたのがこれ。

この辺が第2ポールになるようです。 ミラー効果がなく、両側のインピーダンスも低いので、かなり大きな容量を入れてもそれほどポール周波数が下がりません。 いろいろなところにコンデンサーを入れてみると意外な発見がある、かもしれません。

次にコンデンサを入れる場所を決めます。 コンデンサは、前後のインピーダンスが比較的安定している場所に入れないといけません。 例えば、入力段のゲートにコンデンサを入れると、入力につないだ信号源のインピーダンスでポールの位置が変わってしまい、うまくありません。

で、この回路でインピーダンスと言ったら・・・そもそも、抵抗が2本しかないので、ここ以外はインピーダンスも何もありませんね。 しかも手前は電流源、後ろはMOSFETのゲートしかつながっていないので、どちらもインピーダンスは非常に高く、ほぼこの抵抗でインピーダンスが決まっています。 ついでに、ミラー効果が起きる場所に入れるとコンデンサの容量が小さくて済みます。 この回路の場合、出力段がソース接地で反転出力かつ電圧ゲインがあるので、ミラー効果が発生します。 ということで、ここ以外考えられません(笑)。

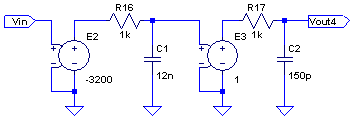

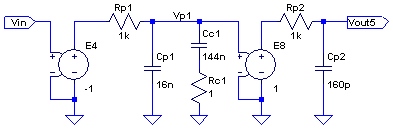

ここは第1ポールですから、補償方法はラグリード補償になります。 ラグリード補償は第1ポールにこんな回路を入れます。

Cc1は大きな値を、Rc1はかなり小さな値を入れます。 定数は分かりやすいように変えました。Rp1・Cp1が第1ポールで10kHzです。Rp2・Cp2が第2ポールで1MHzです。 余談ですが、16という数字は覚えておくといいです。 2π×16がほぼ100になるので。

実際の特性を見る前に、どういう特性になるか考えてみます。 Rp1・Rc1・Cp1・Cc1の回路だけ考えると、周波数が低い範囲ではRc1のインピーダンスよりCc1のインピーダンスの方が大きく無視できるので、Rp1と(Cp1+Cc1)で決まる周波数までほぼ平らの特性になり、その後、6dB/Octで下がっていきます。 この図ではCc1をCp1の9倍に選んでいるので、第1ポールの1/10、つまり1kHzからゲインが下がり始めます。 そして、Cc1のインピーダンスがRc1と同じになったあたりでは、Cp1のインピーダンスはRc1よりもまだずっと大きいので、Cp1はオープン、Cc1はショートとみなすことができ、これはただの抵抗分圧回路で1/1000(-60dB)のゲインになります。 このときの周波数は約1.1MHzになります。 さらに周波数が上がり、Cp1のインピーダンスがRc1と同じになると、Cc1・Rc1がオープンとみなしてよいので、また6dB/Octで下がっていきます。 このときの周波数は10MHzになります。

| 場所 | 関係する抵抗 | 関係する容量 |

|---|---|---|

| 低い側のポール | Rp1 | (Cp1+Cc1) |

| 平らになる場所 | Rc1 | Cc1 |

| 平らな部分のゲイン | Rp1 Rc1 | − |

| 高い側のポール | Rc1 | Cp1 |

実際に見てみます。

緑の線が第1ポールだけの特性、赤の線がRc1・Cc1を入れた特性です。 予測どおりです。 最初のポールの前後で位相が遅れ始め(lag)、平らになると逆に位相が進む(lead)方向へ戻っていきます。 ここでもしCc1を変えると、最初の下がり始めの周波数と平らになる周波数が連動して変わるので、左側の斜めの部分が左右に動くことになります。

赤がCc=144n、黄色はCc=1600n-16n=1584n で、下がり始めがさらに1/10になります。 Rc1を変えると平らになり始める部分と、平らな部分のゲインが連動して変わるので、平らな部分が上下に平行移動するはず。

緑が1Ω、赤が10Ω、黄色が100Ωです。

これに第2ポールの特性を重ねるのですが、もし、平らになる周波数が第2ポールと一致したらどうなるでしょう? 低くなった第1ポールから6dB/Octで下がってきて、第1ポール側は平らになり、入れ替わりで第2ポール側が6dB/Octで下がっていくので、全体では引き続き6dB/Octで下がっていくことになります。 そして、第1ポール側が再び6dB/Octで下がる地点で、第2ポールとあわせて12dB/Octで下がっていくことになります。 つまり、第2ポールの出現が平らになった分だけ遅れます。 最初のグラフを見れば分かるとおり、第1ポールが下がった分だけ平らな部分ができるので、第1ポールが下がった分だけ、第2ポールが上がったように見えます。

黄色が元の特性、緑がラグリード補償後の特性です。 第1ポールが1/10になった分、第2ポールが10倍になっていることが分かります。 位相も平らな部分と元の第2ポールで打ち消しあって、90度で平らな部分が伸びていることが分かります。 ゲインが下がると同時に位相が回るのも遅くなるので、第1ポールを下げた以上に位相余裕が増えます。 一石二鳥。

もし、平らな部分が第2ポールより後ろへ行ってしまうと、途中に12dB/Octの部分が出てきてしまってうまくありません。 ゲインが下がるのは早くなるかもしれませんが、位相が回るのがそれ以上に早くなって位相余裕は取れなくなります。 逆に、平らな部分を第2ポールより前に持ってくると、位相が90度より進む部分ができて位相余裕が増えそうですが、実際には0dBになるのが遅くなって、その部分では元より位相が遅れてますから、結局、位相余裕は取れません。 欲張りはイケマセン。

赤が平らな部分を第2ポールと合わせたもの、緑は遅くしたもの(Rc=0.1Ω)、黄色は早くしたもの(Rc=10Ω)です。 もし、このアンプのゲインが80dBあったとすれば、赤は位相余裕を50度以上とれます。 緑は0dBになるのは早くなりますが、位相が早く遅れてしまい、位相余裕は30度くらいしかありません。 黄色は0dBになるのが遅くなって、0dBになるころにはとっくにリードの部分が終わっているので、かえって位相余裕は悪化して10度くらいしかありません。

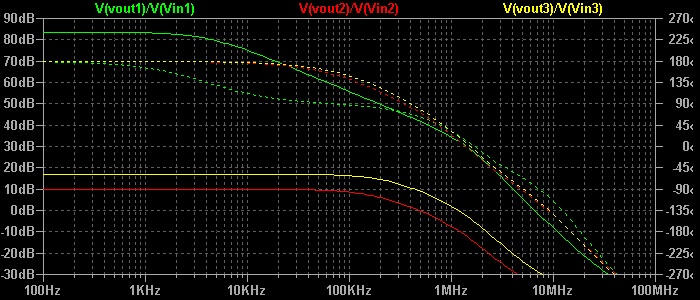

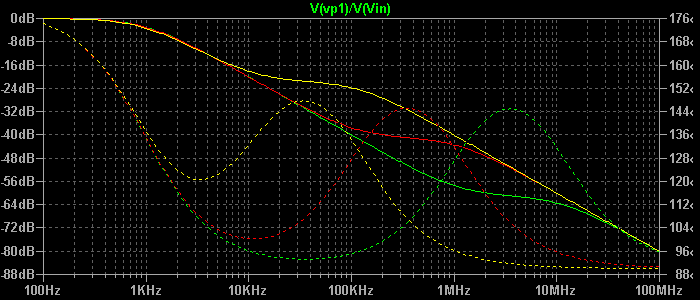

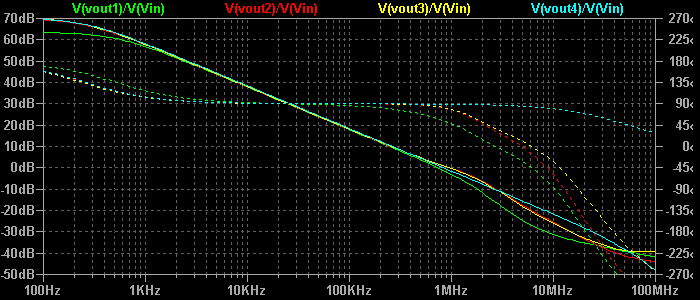

もう一度、実際の特性の図に戻ります。

今度はA級動作時のラインも入れてあります。 位相余裕45度くらいの位置を見ると、30〜40dBゲインがあります。 ここを0dBにしたいので、全体のゲインを30〜40dB下げる必要があります。 ここでは34dB下げる(1/50にする)ことにします。 第1ポール以降は周波数10倍で20dB下がる(1/10になる)ので、34dB下げるには第1ポールの周波数を1/50の位置まで下げなければなりません。 ここで普通は何pFを入れるかとか計算するのですが、ポールの実際の容量を調べるのは面倒なので、値がはっきり分かっている近似曲線でポールを下げて、そこに合わせるように実際の回路にコンデンサを入れていきます。 行き当たりばったり。

周波数を1/50にしたいので、近似曲線の第1ポールのコンデンサ12nFを50倍した600nFを、ポールのコンデンサと並列に入れます。 本当は49倍ですが、細かいことは言わない。 第2ポールと平らになる部分を合わせたいので、Rc1・Cc1の時定数を第2ポールの時定数と合わせます。 Rc1×600nF=1kΩ×150pFなので、Rc1=0.25オームです。

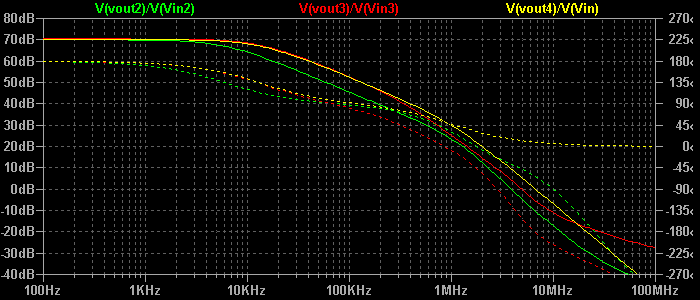

特性はこうなります。

予定通り位相余裕45度の位置で0dBになりました。 第1ポールが1/50になった分、第2ポールが50倍、グラフぎりぎりの50MHzまで高くなっていることが分かります。 これに他の線を合わせていきます。 第1ポールを落とすにはそれなりに大きなコンデンサを入れる必要がありますが、ミラー効果があるので、実際にはコンデンサの容量は1/(|A|-1)倍、抵抗は(|A|-1)倍になります。 N型・P型とも2.2nFを入れたらすべての線がほぼ重なりました。

この状態では位相余裕はほとんどありません。 さらに抵抗を直列に入れます。 N型に110Ω、P型に150Ωを入れてみました。

するとあら不思議、第2ポールが上に移動して、あっという間に位相余裕が増えます。 このときのftは約1MHz、位相余裕は70〜80度あります。 シングル動作時はいい感じですが、A級動作時の位相余裕が少し足りないようにも見えるので、もう少しバランスを探ってみます。

N型を130Ω、P型を180Ωにしてみました。 シングル動作では少し山ができますが、A級動作時の第2ポールは先に伸びました。 A級動作時はft=780kHzで位相余裕70度弱、シングル時はft=1MHzで位相余裕80度です。 ちなみに、抵抗値はE24系列(実際に売ってる抵抗値の数列)で調整していくと、ほぼ同じ比率で値を変更できて便利です。

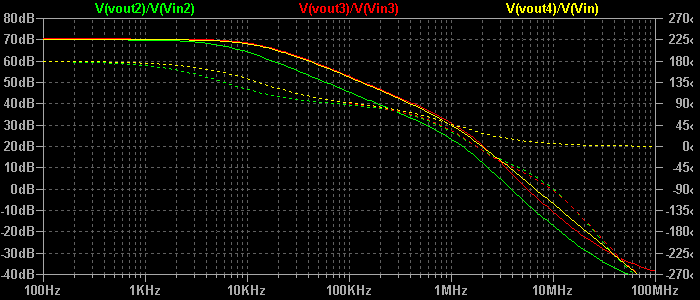

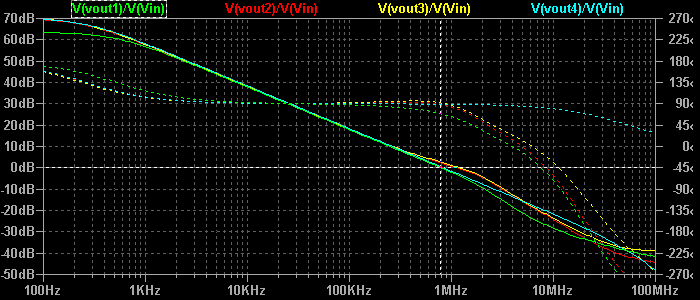

負荷抵抗を10kΩにしてみます。 入力は振幅2.5V±10uVのまま、入力に加えるオフセットは1/10の±0.1mVにします。

出力を±1.5Vしてみたら、なんだかきれいに揃ってしまいました。 振幅はすべて約16mV p-pなので、約800倍。 最初に測定したときよりゲインが下がっているのは位相補償を入れたからですね。 周波数特性はこんな感じ。

問題なさそうです。 回路図をまとめておきます。

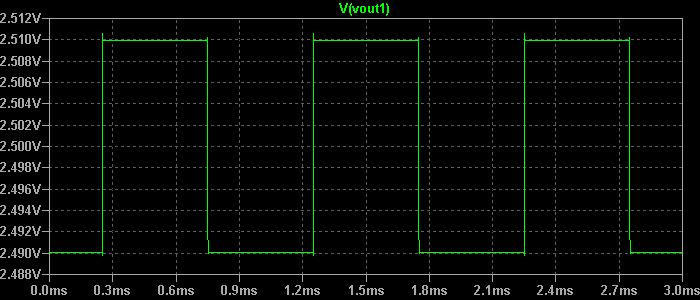

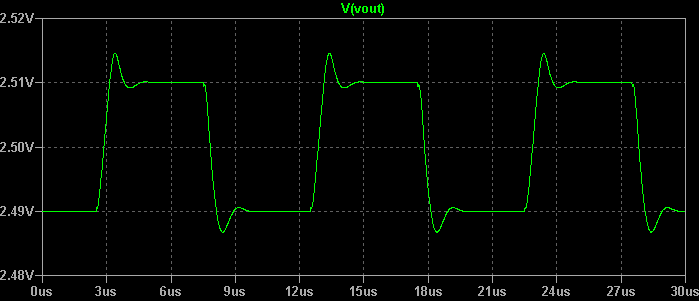

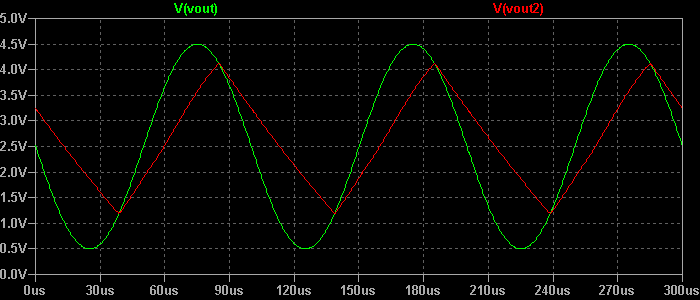

実際に負帰還をかけてみます。 いきなり入力抵抗が1kΩ、帰還抵抗が1kΩの-1倍いってみましょう。

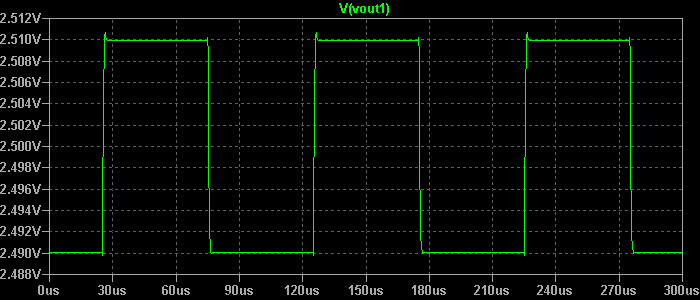

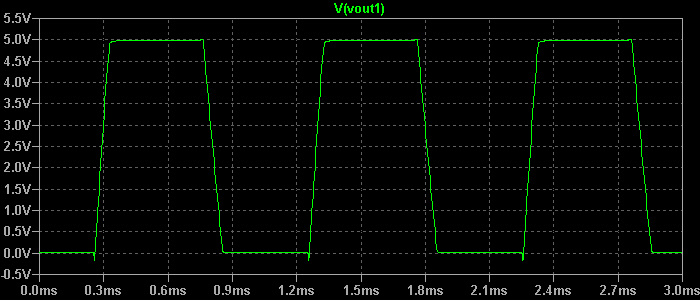

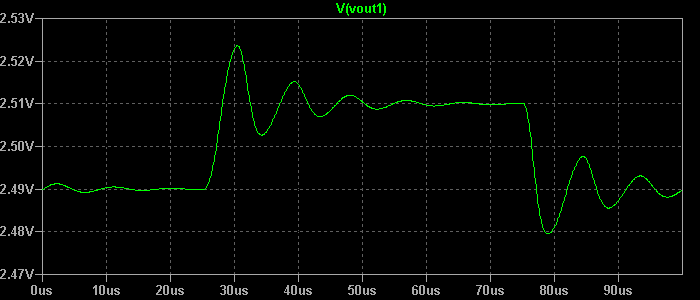

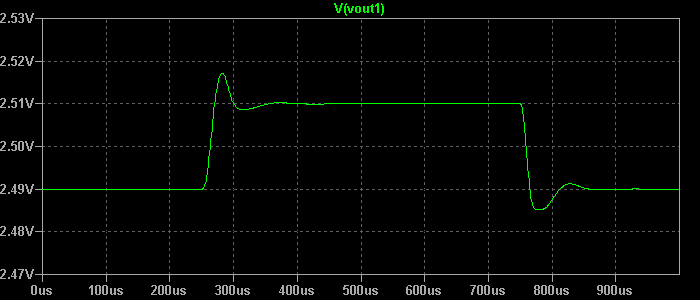

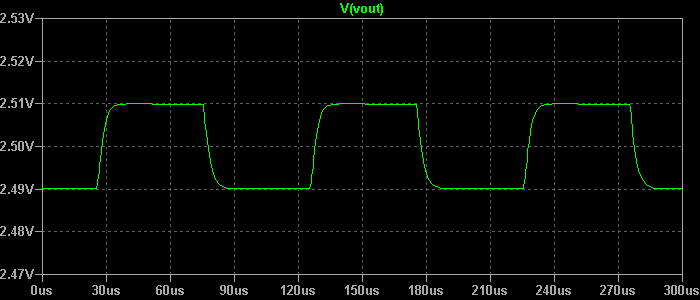

1kHz・±10mV

1kHz・±1V

10kHz・±10mV

10kHz・±1V

ちょこっと立ち上がり・立下りにヒゲが出ますが、非常に安定しています。 パルスの立ち上がり・立下りを1nsにしているので、立ち上がりを遅くするか、フィードバック回路にコンデンサを入れる(LPFにする)かすればなくなります。 フィードスルーかな。 スルーレートは早いところで80mV/us、遅いところで50mV/us弱です。 かなり遅い部類。

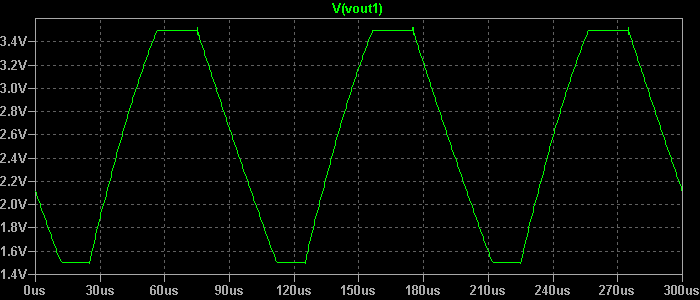

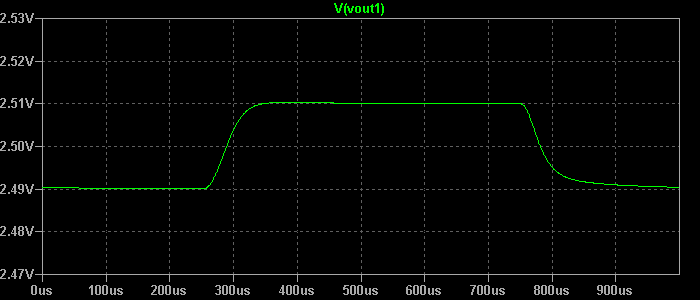

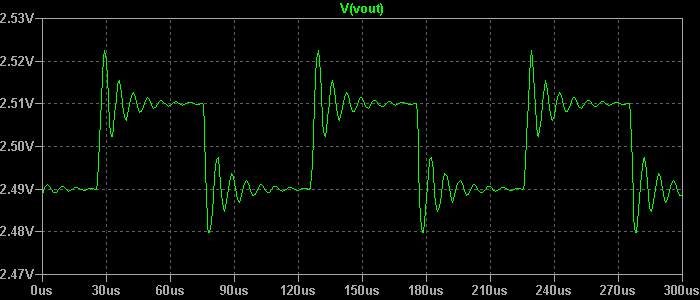

10kHz・1V±100mV

10kHz・4V±100mV

オフセットをかけてみました。 負荷は2.5Vにつないでいます。 上はN型が頑張っている部分で、スルーレート30mV/us前後、下はP型ががんばっている部分で、35mV/us前後。 N型の方が波形が丸いのは、充放電経路に差があるのか、それともN型のゲートが重いのか。

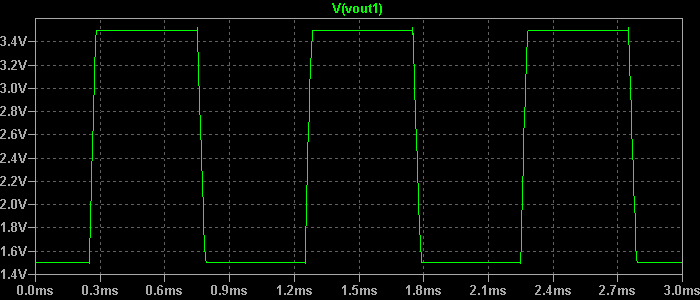

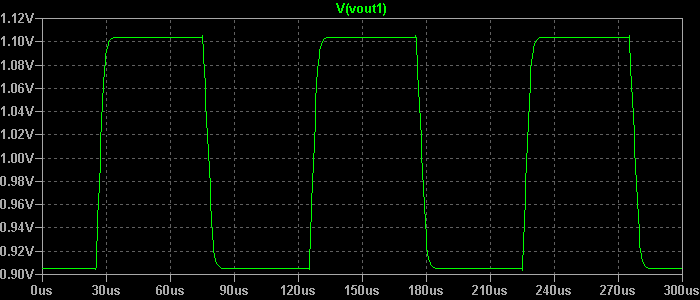

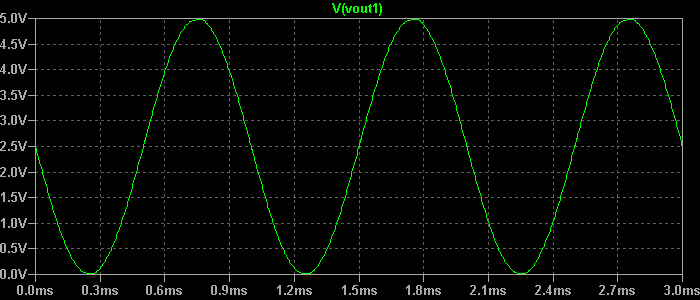

いずれも1kHz・2.5V±2.5V・負荷10kΩ

見事レール to レール。 容量をつなげてみます。

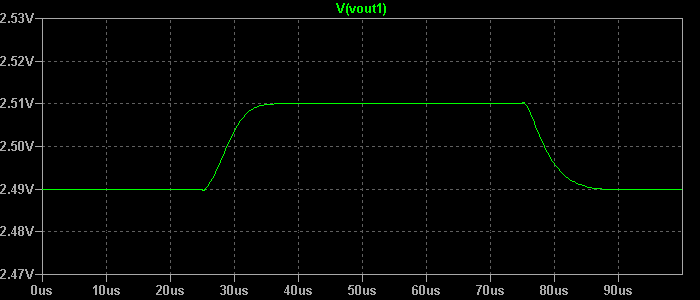

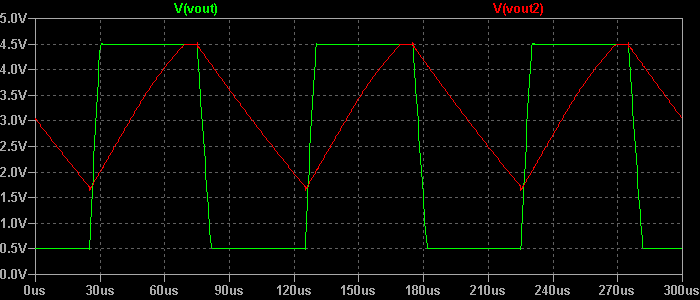

10kHz・2.5V±10mV・負荷1000pF

10kHz・2.5V±10mV・負荷0.01uF

10kHz・2.5V±10mV・負荷0.1uF

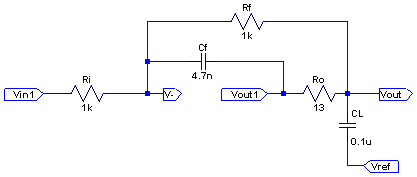

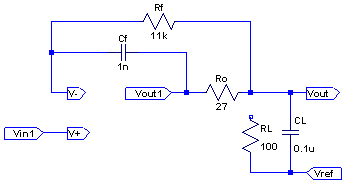

1000pFくらいからリンギングが出始めて、容量を大きくするに従って振幅は大きく、周期は長く、波数も多くなっていきます。 0.1uFくらいで一番ひどくなりますが、発振する様子はありません。 これを抑えるにはこんな回路を入れます[1]。

参考資料には2πfT・CLRO=2πfT・CLRF=1 になるように選べ、と書いてあるのですが、どうもうまくいかないので、定数はこれまた行き当たりばったりです。 具体的には、まずCFを入れます。 大きくしていくとリンギングはそのままでオーバーシュートが下がっていき、だらだらと上昇しながら減衰振動するようになるので、オーバーシュートがなくなるまで容量を増やします。 これでCRの充放電波形になればそれでOK。 ならない場合はROを入れて徐々に大きくしていくとリンギングが減って行きます。 あまり大きくすると今度はオーバーシュートが復活します。

実際の波形です。 帯域幅は犠牲になりますが、リンギングはきれいになくなりました。 この手は普通のOPアンプでも使えます。

0.1uFを超えると周期は長くなりますがオーバーシュートは小さくなってきて、10uFでは一発で収まるようになります。

1kHz・2.5V±10mV・負荷1uF

1kHz・2.5V±10mV・負荷10uF

1kHz・2.5V±10mV・負荷100uF

容量に比例して周期が長くなるので、この3枚は周波数1kHzです。

反転増幅器の最後はひずみ率。 SPICEディレクティブはこんな感じ。

.options plotwinsize=0

.param f=1k fs=f*256 Ts=1/fs

.tran 0 {12/f} 0 {Ts}

.step param f 1k 10k

.step param amp list 1m 1.5m 2m 3m 4m 5m 7m 10m 15m 20m 30m 40m 50m ...

.four {f} 9 8 V(Vout)

こうすると1周期を256分割して12周期分計算し、後ろ8周期で第9高調波までのひずみ率を求めてくれます。

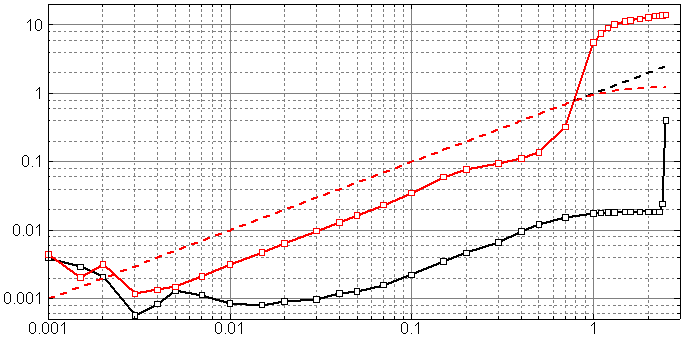

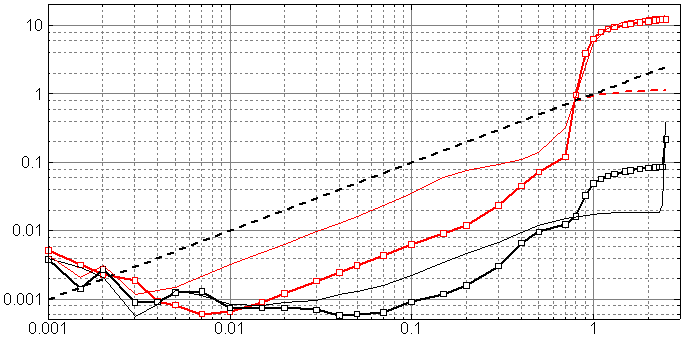

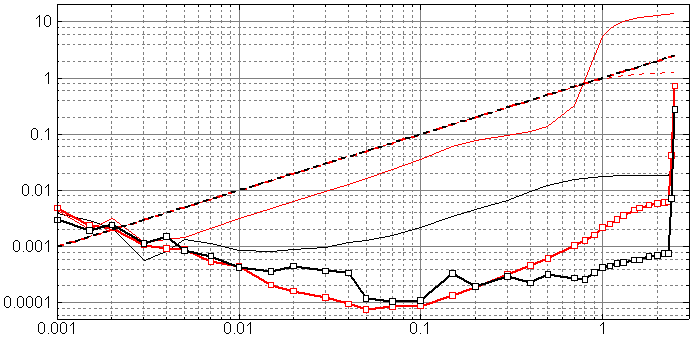

黒は1kHz、赤は10kHzです。 横軸は入力電圧振幅[V]、実線はひずみ率[%]、点線は出力電圧振幅[V]です。 負荷は1kΩ。 低いレベルでひずみ率がうろちょろするのはノイズの影響か、サンプル数の問題でしょうか。

1kHzは小振幅時のひずみ率がだいたい0.001%。 0.1VあたりからAB級動作となり、徐々にひずみが増えていきます。 最終的に1V程度でひずみ率は0.02%程度に落ち着きます。 この辺が完全にB級動作になったあたりでしょうか。 素の状態のひずみは増えますが、ゲインが増えている分だけNFB量が増えるので、トータルのひずみ率はそんなに悪化しません。 入力0Vに対しては出力0V、入力5Vに対しては5Vの出力が出るので、2.5V±2.5Vの入力に対して、出力はきっちり2.5V±2.5Vになります。 2.4Vを超えると急にひずみ率が悪化しますが、それでも1%は超えていません。

それに対して、10kHzは1kHzに比べてNFBが減った分だけひずみ率が悪化し、さらに スルーレートの関係で最大振幅が1Vちょっとしか出ません。 0.5Vを越えたあたりから急激にひずみ率が悪化しますが、これはスルーレートが追いつかなくなって出力がどんどん三角波に近づいているからです。

今度は入力を正相(非反転)入力に直結、出力を逆相(反転)入力に直結のボルテージフォロアです。 長くなったので特徴的な部分だけ。

100kHz・2.5V±10mV・負荷1kΩ

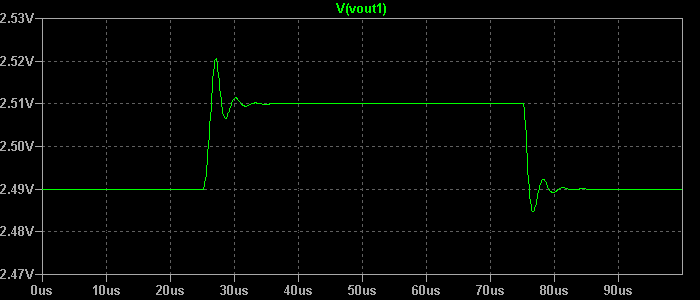

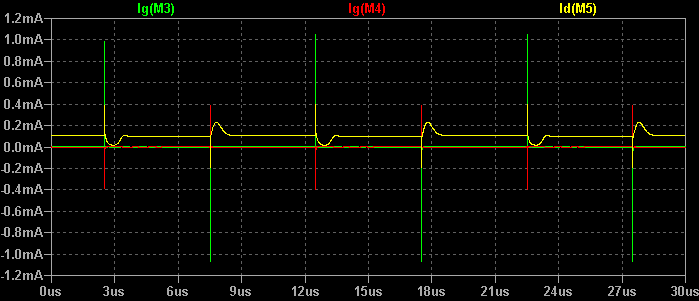

100kHz・10mV p-pです。 位相余裕は問題ありませんが、立ち上がり・立下りに切れ込み状のヒゲが入っています。 これは入力からのフィードスルーです。 どういう経路か探してみると、V+から入力FETのゲート−ソース間容量を通って、それがV-側のFETのゲート−ソース間容量を通り、そのままV-から出てきて、帰還回路を通って出力へ流れ込んでいます。 特にスパイク状の電流が大きいところを拾い出してみるとこんな感じでした。

入力が立ち上がったときを見てみると、V+入力につながっているM3のゲートに1mAもの電流が流れ込んでいます(緑線)。 この電流を追いかけてみると一部はドレイン側に流れますが、ソース側へ700uA流れ、うち100uAは定電流源に流れてM4のソースへ600uA流れ込みます。 600uAのうち200uAはM4のドレインに流れますが、残り400uAがゲートから出てきます(赤線)。 M4のゲートはV-入力で、ここには帰還回路しかつながっていませんから、帰還回路を通って出力側へ逆流していきます。

負荷には10mV/1kΩ=10uAしか流れていないので、ほとんどは出力のMOSFET M5・M6のゲート−ドレイン間容量の充電に使われます。 M5はN型MOSFETで、出力が10mVならA級動作しているので、定常的に流れているドレイン電流100uAはP型から来たものです。 400uAから100uAを引いて、スパイク状になっている部分300uAがゲート−ドレイン間容量をチャージしている電流です(黄色)。 残りの100uAはP型MOSFETの方をチャージしています。 結果として出力に正のスパイクが現れます。 入力の立ち下りではこれと逆の現象が起き、負のスパイクが発生します。

電流の経路が分かれば対策は意外と簡単で、充電経路に抵抗を入れれば収まります。 試しにV+入力に1kΩを入れてみました。

V+入力に1kΩを接続

帰還回路に抵抗を入れるとV-の寄生容量との間で時定数ができるので、位相余裕は悪化します。 同じ値の抵抗ならV+側に入れた方がよいようです。 バイアス電流によるオフセットを考慮する場合は、V+とV-に同じ値の抵抗を入れることになっていますが、今はMOSFETなのであまり関係ありません。 V+側なら位相余裕に影響を与えないかというとそうでもないらしく、今度はチャージされた電荷が抜けるのに時間がかかるようになるので、その分だけオーバーシュートが大きくなります。 また、あまり抵抗を大きくしすぎると、V+の寄生容量との時定数が大きくなって周波数特性が悪化します。

差動増幅器のソース側(全部で4箇所)に100Ω程度の小さな抵抗を入れるのも効果があります。 ただし、ゲインが下がるのでその分だけftも下がり、周波数特性は悪化します。 位相特性は変わらないので、位相余裕は逆に増加します。 位相補償の値を調整すれば差は縮まると思いまが、ゲインが下がるということは負帰還の量も減るので、出力段由来のひずみは悪化すると思います。

容量をつないでみました。

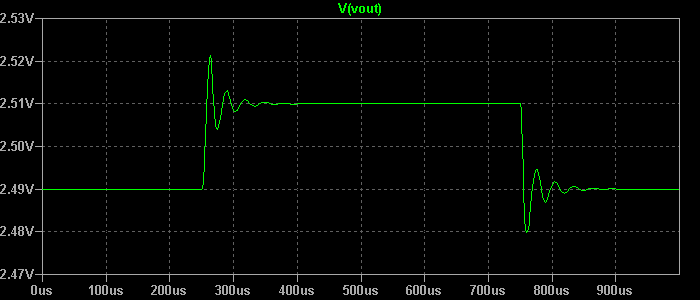

10kHz・2.5V±10mV・負荷0.1uF

反転1倍よりひどいです。 非反転の場合も基本的には反転の場合と同じように対策できるのですが、ボルテージフォロアの場合は逆相(反転)入力端子に抵抗がつながっていないので、なかなかうまく調整できません。

やり方としては、まずRoを入れます。 運がよければこれだけでうまく収まります。 しかし、RLをつないでしまうと、その分だけ電圧が下がってしまいます。 そこで、直流的にはRfでフィードバックをかけ、交流的にはCfで位相を進めることで解決します。 どうもRf・Cfの時定数をRL・CLとほぼ同じにするといいようです。 あとは適当に微調整すると、いいところが見つかります、たぶん。 RLによっても定数は変わってきます。 上の定数でRLを接続すると、以下のような出力になります。

10kHz・2.5V±10mV・負荷100Ω//0.1uF

なんとかなりました。

ひずみ率です。

太線は非反転、細線は反転増幅器。黒は1kHz、赤は10kHz、実線はひずみ率、点線は出力電圧。 こうしてみると、全体的に非反転のほうがひずみ率が低いです。 理由はヨクワカリマセン。 反転増幅器の帰還抵抗を若干大きくするとひずみ率が改善するので、非反転増幅器は負荷抵抗と入力容量をドライブすればよいのに対し、反転増幅器では帰還抵抗−入力抵抗もドライブしなければならないのが効いているのかもしれません。

1kHzで急にひずみ率が悪化して反転増幅器と逆転するところがありますが、これは入力段がP型のみ・N型のみの部分に達する場所と思われます。 10kHzではスルーレートの不足によるひずみの増加の方が目立ちます。 出力電圧の傾向は反転・非反転ともほぼ同じです。

最後に、冒頭のEDN Japan / オペアンプ回路のTHD+Nに書いてあった現象を確かめてみます。 入力電圧対ひずみ率を求めることになるのですが、出力段の条件を同じにするため、出力電圧が同じになるようにゲイン(つまりフィードバック抵抗の値)も動かします。 出力電圧が4V p-pになるように測定したのが以下のグラフ。 周波数1kHz、負荷抵抗は1kΩで、反転増幅器では入力抵抗を、非反転増幅器では反転入力−基準電位間の抵抗を1kΩにしてあります。

黒が反転、赤が非反転増幅器。 横軸は入力電圧振幅[V]、縦軸はひずみ率[%]。 入力電圧が上がるとひずみはきれいに下がっていくのですが、非反転増幅器は0.7Vを超えたあたりから急激にひずみが増えます。 これは入力が差動増幅対のN型のみ・P型のみの動作領域まで達するからです。 対照的に、反転増幅器の場合は両入力端子ともほぼ基準電位になるため、常にN型+P型の領域で動き、このようなひずみ率の悪化はありません。 エラそうに書いてるけど初めて知った(笑)。

現実のOPアンプの規格を見ると、このほかにも温度特性やらCMRRやらPSRRやらいろいろあるのですが、やってるとキリがないのでとりあえずこの辺にしておきます。 誰かやってみておくれ(笑)。

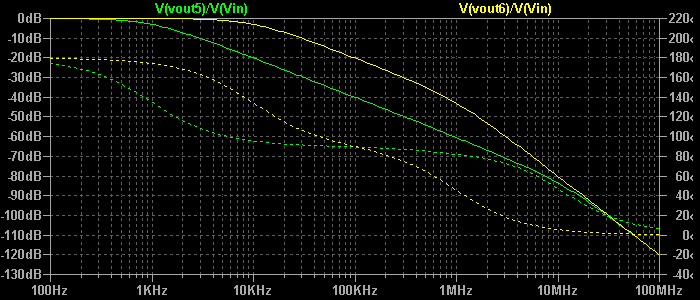

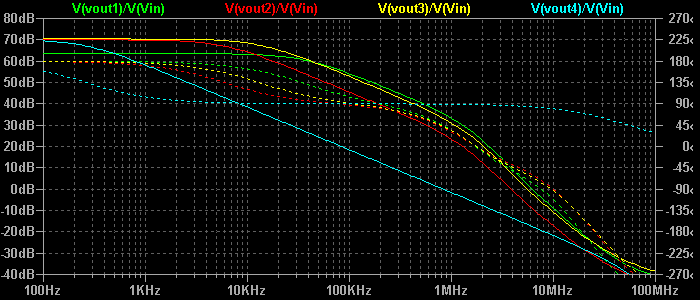

設定電流を全部10倍、つまり1mAにしてみました。 オフセット調整をしているI6は993.52uAになり、この状態での位相補償をしない開放利得はこんな感じ。

緑が1mA、赤が100uA。 ゲインが全体に20dB近く上がっています。 これは当然と言えば当然で、今まで出力段の抵抗を±100uAでドライブしていたのが±1mAになったので、10倍になります。

第1ポールは10kHz前後、第2ポールは4MHzくらいのところにあります。 出力段には第1ポールがあり、ミラー効果があるので、ゲインが上がった分、ポールの位置が低い周波数にずれています。 でも1/10になっているわけではなさそう。 第2ポールは高い方へずれました。

この状態で位相補償のコンデンサは2nF、抵抗は51Ωとなりました。 ポールは下がっているので、実質の補償容量はその分大きくなりますが、ゲインが上がってミラー効果も大きくなっているので、全体としては容量はほぼそのまま。 第2ポールが上がった分、抵抗値は小さくなりました。 位相補償後の特性はこんな感じ。

100uAのときよりも周波数特性が上に伸びています。ftは約3MHz、位相余裕は70度弱です。 反転1倍の大振幅レスポンス。 入力抵抗・フィードバック抵抗、負荷、すべて1kΩ。

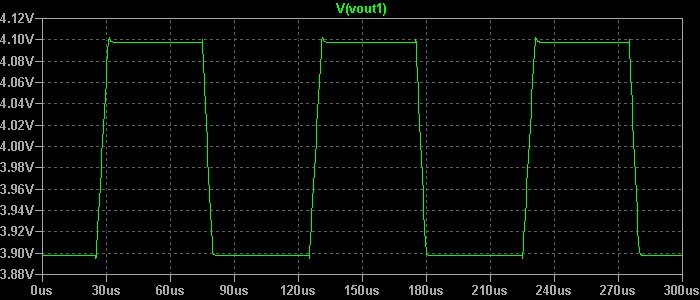

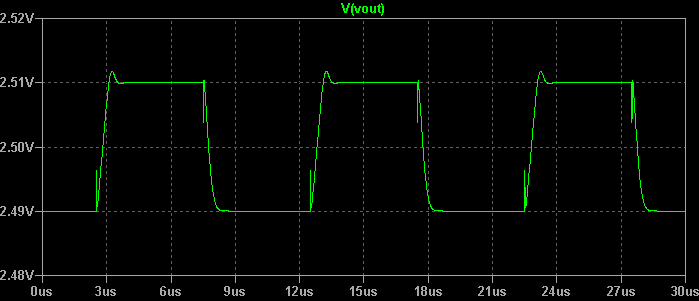

10kHz・2.5V±2V・負荷1kΩ

10kHz・2.5V±2V・負荷1kΩ

緑線がバイアス1mA、赤線は同じ条件でバイアス100uA。 すぐに分かるのはスルーレートが格段に大きくなっていることです。 0.6V/usくらい。 ほぼ10倍。 出力段のゲート容量を10倍の速度でチャージできるからですね。

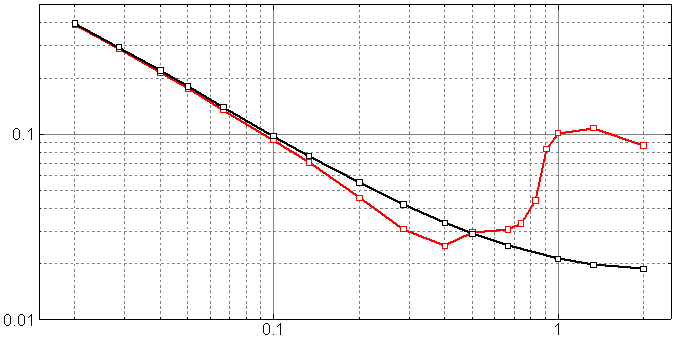

ひずみ率。

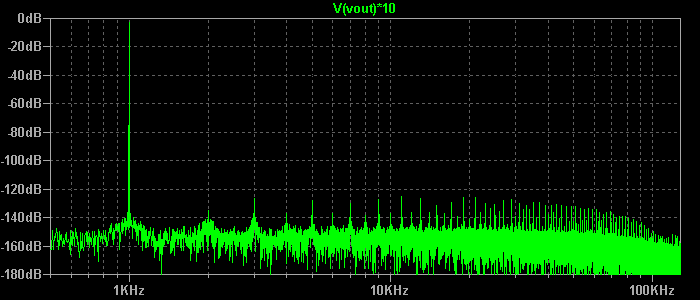

負荷1kΩ、横軸は入力電圧[V]、実線はひずみ率(左軸[%])、破線は出力振幅(左軸[V])、黒は1kHz、赤は10kHz。 太線はバイアス1mA、細線は100uA。 ゲインが増えたのと、出力段のバイアスが増えたので、ひずみ率は大幅に改善。 NFB量が1kHzと10kHzで20dB違うので、ひずみ率も1ケタ違います。 10kHzで改善が著しいのはスルーレートが改善したから。 出力振幅も±2.5Vのフルスケールに達しています。 0.1V近辺で特性が暴れるのはシミュレーションの限界でしょうか? そう思って入力0.1VでFFTをとってみると、

高調波は-120dB以下でしたとさ。 電圧が低いところでひずみ率が改善しないのはフロアノイズの影響みたいですね。

[1] 玉村俊雄著 OPアンプIC活用ノウハウ CQ出版社 1983年12月初版、1986年2月第5版 ISBN4-7898-3071-3

Copyright (C) 2014 You SUZUKI

$Id: index.htm,v 1.2 2014/03/16 11:35:49 you Exp $